# NASA Langley's Research and Technology-Transfer Program in Formal Methods

Ricky W. Butler

Victor A. Carreño

Ben L. Di Vito

Kelly J. Hayhurst

C. Michael Holloway

Jeffrey M. Maddalon

Paul S. Miner

César Muñoz (ICASE)

Alfons Geser (ICASE)

Hanne Gottliebsen (ICASE)

Assessment Technology Branch NASA Langley Research Center Hampton, Virginia

http://shemesh.larc.nasa.gov/fm.html

May 2002

#### Abstract

This paper presents an overview of NASA Langley's research program in formal methods. The major goals of this work are to make formal methods practical for use on high integrity systems, to orchestrate the transfer of this technology to U.S. industry through use of carefully designed demonstration projects, and to exploit this technology to help achieve NASA's goals in aeronautics. Several direct technology transfer efforts have been initiated that apply formal methods to critical subsystems of real aerospace computer systems.

# Contents

| 1 | Rat | ionale For a Formal Methods Research Program                                  | 4  |

|---|-----|-------------------------------------------------------------------------------|----|

|   | 1.1 | The Problem With Software and Hardware                                        | 5  |

|   | 1.2 | What is Formal Methods                                                        | 6  |

|   |     |                                                                               |    |

| 2 | Goa | ds of Our Program, Strategy, and Research Team                                | 7  |

|   | 2.1 | Scope of Effort                                                               | 7  |

|   | 2.2 | Technology Transfer                                                           | 7  |

| _ | _   |                                                                               | _  |

| 3 |     | ent Technology Development and Transfer Projects                              | 8  |

|   | 3.1 | Formal Analysis of Air Traffic Management Systems                             | 8  |

|   | 3.2 | Formal Analysis of AILS                                                       | 9  |

|   | 3.3 | Scalable Processor-Independent Design for Electromagnetic Resilience (SPIDER) | 9  |

|   | 3.4 | v e                                                                           | 10 |

|   | 3.5 |                                                                               | 11 |

|   |     | 8                                                                             | 11 |

|   |     | <i>'</i>                                                                      | 12 |

|   |     | 3.5.3 Object Oriented Technology in Aviation                                  |    |

|   |     | 3.5.4 PVS Strategies                                                          |    |

|   | 3.6 |                                                                               | 13 |

|   |     |                                                                               | 13 |

|   |     |                                                                               | 13 |

|   |     | •                                                                             | 14 |

|   | 3.7 |                                                                               | 15 |

|   | 3.8 | 1                                                                             | 15 |

|   |     |                                                                               | 15 |

|   |     | •                                                                             | 16 |

|   |     |                                                                               | 17 |

|   |     | 3.8.4 PVS Classes                                                             | 17 |

|   | _   | . 7.0                                                                         |    |

| 4 |     |                                                                               | 18 |

|   | 4.1 | Fundamental Research                                                          |    |

|   |     | 4.1.1 Streamlining Software Aspects of Certification                          |    |

|   |     | 4.1.2 Formal Methods Analysis of Mode Confusion                               |    |

|   |     | · · · · · · · · · · · · · · · · · · ·                                         | 19 |

|   |     |                                                                               | 20 |

|   |     |                                                                               | 20 |

|   |     |                                                                               | 20 |

|   |     | •                                                                             | 20 |

|   |     | 9                                                                             | 21 |

|   |     |                                                                               | 21 |

|   | 4.2 | v ov v                                                                        | 22 |

|   |     | ,                                                                             | 22 |

|   |     | <u>o</u>                                                                      | 22 |

|   |     |                                                                               | 23 |

|   |     | 9                                                                             | 23 |

|   |     | 4.2.5 Verification of Existing Ada Applications Software                      | 24 |

|                          |     | 4.2.6   | Asynchronous Communication                      | 24 |

|--------------------------|-----|---------|-------------------------------------------------|----|

|                          |     | 4.2.7   | Digital Design Derivation                       | 24 |

|                          |     | 4.2.8   | NASA Small Business Innovative Research Program | 24 |

|                          |     | 4.2.9   | Union Switch and Signal                         | 25 |

|                          |     | 4.2.10  | CSDL Scoreboard Hardware                        | 25 |

|                          |     | 4.2.11  | Allied Signal's Hybrid Fault Algorithms         | 25 |

|                          | 4.3 | Fault-t | tolerant Systems                                | 26 |

|                          |     | 4.3.1   | The Reliable Computing Platform                 | 26 |

|                          |     | 4.3.2   | Clock Synchronization                           | 27 |

|                          |     | 4.3.3   | Byzantine Agreement Algorithms                  | 28 |

| 5                        | Coc | ordinat | ion Activities                                  | 29 |

|                          | 5.1 | Relatio | onship to NASA Program Offices                  | 29 |

| 5.2 FAA/RTCA Involvement |     |         |                                                 |    |

| 6                        | Sun | nmary   |                                                 | 30 |

# 1 Rationale For a Formal Methods Research Program

NASA Langley Research Center has been developing techniques for the design and validation of flight critical systems for over two decades. Although much progress has been made in developing methods to accommodate physical failures, design flaws remain a serious problem [85, 112, 57, 1, 77, 49, 124].

The following recent events show the potential of design errors for disaster:

- The maiden flight of the Ariane 5 launcher (June 4 1996) ended in an explosion. Total loss was over \$850 million.

- Between June 1985 and January 1987, a computer-controlled radiation therapy machine, called the Therac-25, massively overdosed six people, killing two.

- Replacement of defective Pentium processors costs Intel Corp. \$475 million in 1995.

- The April 30, 1999 loss of a Titan I, which cost the taxpayers \$1.23-billion, was due to incorrect software (incorrectly entered roll rate filter constant)

- December 1999 loss of the Mars Polar Lander was due to an incomplete software requirement. A landing leg jolt caused engine shutdown.

- Denver Airport's computerized baggage handling system delayed opening by 16 months. Airport cost was \$3.2 billion over budget.

- Patriot failure at Dharan (software error put tracking off by 0.34 of a second)

A January 24, 1999 report from the Office of Science and Technology Policy entitled Information Technology For The Twenty-First Century: A Bold Investment In America's Future states

Software research was judged by The President's Information Technology Advisory Committee to be the highest priority area for fundamental research. From the desktop computer to the phone system to the stock market, our economy and society have become increasingly reliant on software. This Committee concluded that not only is the demand for software exceeding our ability to produce it; the software that is produced today is fragile, unreliable, and difficult to design, test, maintain, and upgrade.

Although the aviation industry has been more conservative and cautious in its adoption of information technology than most other industries, it is beginning to suffer from the effects of software. David W. Robb (editor) writes in the Oct 1996 issue Avionics Magazine:

Avionics have never been more clearly at center stage. The benefits of flat-panel and heads-up displays, the precision of GPS positioning, ... and the flexibility of integrated avionics, to name just a few areas, are transforming aviation almost faster than we can print these words.

It is no secret that aircraft are becoming ever more dependent on their onboard electronics. The emerging world of CNS and Free Flight promises to accelerate this trend dramatically. As the equipment grows more capable and sophisticated, so does the challenge of testing and maintaining it.

Harry C. Stonecipher, President and Chief Operating Officer The Boeing Company. wrote in an article entitled "Getting It Right: Defense Acquisition for the 21st Century" May 26, 1999:

... avionics systems account for about one-third of the fly-away cost of a military aircraft and a significant amount of its life-cycle cost. It goes without saying that our warfighters are increasingly dependent upon the use of avionics systems for everything from navigation to targeting and to battlefield management.

## 1.1 The Problem With Software and Hardware

Digital systems (both hardware and software) are notorious for their unpredictable and unreliable behavior:

Studies have shown that for every six new large-scale software systems that are put into operation, two others are canceled. The average software development project overshoots its schedule by half; larger projects generally do worse. And three quarters of all large systems are "operating failures" that either do not function as intended or are not used at all.

Despite 50 years of progress, the software industry remains years—perhaps decades—short of the mature engineering discipline needed to meet the demands of an information-age society[52].

Lauren Ruth Wiener describes the software problem in her book, Digital Woes: Why We Should Not Depend Upon Software:

Software products—even programs of modest size—are among the most complex artifacts that humans produce, and software development projects are among our most complex undertakings. They soak up however much time or money, however many people we throw at them.

The results are only modestly reliable. Even after the most thorough and rigorous testing some bugs remain. We can never test all threads through the system with all possible inputs [156].

The hardware industry also faces serious difficulties, as evidenced by the 1994 design error in the Pentium floating-point unit. In response to an outcry over the design flaw in the Pentium floating point unit, Intel's President, Andy Grove, wrote on the comp.sys.intel Internet bulletin board:

After almost 25 years in the microprocessor business, I have come to the conclusion that no microprocessor is ever perfect; they just come closer to perfection with each stepping. In the life of a typical microprocessor, we go thru [sic] half a dozen or more such steppings....

Three basic strategies have been advocated for dealing with the design fault problem for the life-critical system: (1) Testing (Lots of it) (2) Design Diversity (i.e. software fault tolerance: N-version programming, recovery blocks, etc.), and (3) Fault Avoidance (i.e. formal specification/verification, automatic program synthesis, reusable modules). The problem with life testing is that in order to measure ultra-reliability one must test for exorbitant amounts of time. For example, to measure a  $10^{-9}$  probability of failure for a 1 hour mission one must test for more than  $10^9$  hours (114,000 years).

The basic idea of design diversity is to use separate design and implementation teams to produce multiple versions from the same specification. At run-time, non-exact threshold voters are used to

mask the effect of a design error in one of the versions. The hope is that the design flaws will manifest errors independently or nearly so. By assuming independence, one can obtain ultrareliable-level estimates of reliability, even with failure rates for the individual versions on the order of  $10^{-4}$ /hour. Unfortunately, the independence assumption has been rejected at the 99% confidence level in several experiments for low reliability software [80, 81].

Furthermore, the independence assumption cannot be validated for high reliability software because of the exorbitant test times required. If one cannot assume independence then one must measure correlations. This is infeasible as well; it requires as much testing time as life-testing the system, because the correlations must be in the ultrareliable region in order for the system to be ultrareliable. Therefore, it is not possible, within feasible amounts of testing time, to establish that design diversity achieves ultrareliability. Consequently, design diversity can create an "illusion" of ultrareliability without actually providing it. For a more detailed discussion, see [14, 13].

#### 1.2 What is Formal Methods

Engineering relies heavily on mathematical models and calculation to make judgments about designs. This is in stark contrast to the way in which software systems are typically designed—with ad hoc technique and after-implementation testing. Formal methods bring to software and hardware design the same advantages that other engineering endeavors have exploited: mathematical analysis based on models. Formal methods are used to specify and model the behavior of a system and to formally verify that the system design and implementation satisfy functional and safety properties. Formal methods refers to the use of techniques from logic and discrete mathematics in the specification, design, and construction of computer systems (both hardware and software)<sup>1</sup> and relies on a discipline that requires the explicit enumeration of all assumptions and reasoning steps. Each reasoning step must be an instance of a relatively small number of allowed rules of inference. In essence, system verification is reduced to a calculation that can be checked by a machine. In principle, these techniques can produce error-free design; however, this requires a complete verification from the requirements down to the implementation, which is rarely done in practice.

Thus, formal methods is the applied mathematics of computer systems engineering. It serves a similar role in computer design as Computational Fluid Dynamics (CFD) plays in aeronautical design, providing a means of calculating and hence predicting what the behavior of a digital system will be prior to its implementation.

The tremendous potential of formal methods has been recognized by theoreticians for a long time, but the formal techniques have remained the province of a few academicians, with only a few exceptions such as the Transputer [2] and the IBM CICS project [69]. NASA Langley's program has helped to advance the capabilities of formal methods to the point where commercial exploitation is near.

It is important to realize that formal methods is not an all-or-nothing approach. The application of formal methods to the most critical portions of a system is a pragmatic and useful strategy. Although a complete formal verification of a large complex system is impractical at this time, a great increase in confidence in the system can be obtained by the use of formal methods at key locations in the system. For more information on the basic principles of formal methods, see [15].

<sup>&</sup>lt;sup>1</sup> "Formal" means that the methods of reasoning are valid by virtue of their form and independent of their content.

# 2 Goals of Our Program, Strategy, and Research Team

The major goals of the NASA Langley research program are to make formal methods practical for use on high integrity systems developed in the United States, to orchestrate the transfer of this technology to industry through use of carefully designed demonstration projects, and to exploit this technology to help achieve NASA's ambitious goals in aeronautics. Our intention is to concentrate our research efforts on the technically challenging areas of digital flight-control systems design that are currently beyond the state-of-the-art, while initiating demonstration projects in problem domains where current formal methods are adequate. The challenge of the demonstration projects should not be underestimated. That which is feasible for experts that have developed the tools and methods is often difficult for practitioners in the aerospace industry. There is often a long "learning curve" associated with the tools, the tools are not production-quality, and the tools have few or no examples for specific problem domains. Therefore, we are setting up cooperative efforts between industry and the developers of the formal methods to facilitate the technology transfer process.

# 2.1 Scope of Effort

It is important to realize that formal methods include a large class of mathematical techniques and tools. Methods appropriate for one problem domain may be totally inappropriate for other problem

essential that NASA Langley become directly involved in specific problem domains of the aerospace industry. Equally important is the need for industry to make investments to work with NASA on joint projects and help devise realistic and practical demonstration projects. The ultimate goal of our technology transfer process is for formal methods to become the "state-of-the-practice" for developing high integrity digital avionics systems in the United States

Our basic approach to technology transfer is as follows. The first step is to find an industry representative who is interested in formal methods, believes that there is a potential benefit of such methods, and is willing to work with us. The next step is to fund our formal methods research team to apply formal methods to an appropriate application. This process allows the industry representative to see what formal methods are and what they have to offer, and it allows us (the formal methods team) to learn the design and implementation details of state-of-the-practice components so we can better tailor our tools and techniques to industry's needs. If the demonstration project reveals a significant potential benefit, the next stage of the technology transfer process is for the industry representative to initiate an internal formal methods program, and begin a true cooperative partnership with us.

Another important part of our technology transfer strategy is working with the Federal Aviation Administration (FAA) to update certification methods with respect to formal methods. If the certification process can be redefined in a manner that awards credit for the use of formal methods, a significant step toward the transfer of this technology to the commercial aircraft industry will have been accomplished.

Langley has also been sponsoring a series of workshops on formal methods. The first workshop, held in August 1990, focused on building cooperation and communication between U.S. formal methods researchers[18]. The second, held in August 1992, focused on education of the U.S. aerospace industry about formal methods[76]. The third workshop was held in May 1995[63], the fourth in September 1997 [65], and the fifth in June 2000 [64].

Finally, to facilitate technology transfer, much information on NASA Langley's formal methods research is available on the Internet via the World Wide Web at the following location:

http://shemesh.larc.nasa.gov/fm/

# 3 Recent Technology Development and Transfer Projects

# 3.1 Formal Analysis of Air Traffic Management Systems

This work is part of NASA's Aviation System Capacity (ASC) Program that is led by NASA Ames. The objective of the Advanced Air Transportation Technologies (AATT) component of this program is to improve the overall performance of the National Airspace System (NAS). Under AATT, Distributed Air Ground Traffic Management (DAG-TM) is a long-term concept for gate-to-gate NAS operations beyond the year 2015. It will address dynamic NAS constraints such as bad weather, Special Use Airspace (SUA) and arrival metering/spacing. The goal of DAG-TM is to enhance user flexibility/efficiency and increase system capacity, without adversely affecting system safety or restricting user accessibility to the NAS. Current work is looking at the formal analysis of conflict detection and resolution algorithms (CD&R) and merging and self-spacing algorithms that are being developed for the DAG-TM thrust.

A generalization of Karl Bilimoria's CD&R algorithm (used in FACET) to 3 dimensions was accomplished at ICASE[45, 19, 109]. The solution is decomposed into two pieces: CD3D and KB3D, algorithms for conflict detection and resolution, respectively. A conflict is a projected incursion of the intruder aircraft within the protected zone of the ownship. A solution is a single

maneuver, to be performed by the ownship, that effectively keeps the required minimum separation without cooperation of the intruder aircraft. Both algorithms CD3D (Conflict Detection) and KB3D (Conflict Resolution) have been formally verified in PVS [46]. Recently work on optimal return paths has been completed [50].

Current work is also looking at new algorithms for merging and sequencing aircraft in the terminal area.

# 3.2 Formal Analysis of AILS

The Airborne Information for Lateral Spacing (AILS) is a research project within the Reduced Spacing Operations (RSO) element of the Terminal Area Productivity (TAP) Program at NASA. The objective of the AILS research is to increase the ability of aircraft to land on closely-spaced parallel runways in Instrument Meteorological Conditions (IMC). The current minimum runway separation for independent landings during IMC is 4300 feet. Using AILS, independent parallel approaches down to 2500 feet separation are expected to be possible. The AILS system is an airborne alerting system that uses Automatic Dependent Surveillance-Broadcast (ADS-B) datalink and differential GPS.

This inhouse project is exploring the use formal methods to analytically demonstrate that the AILS alerting algorithm complies with its requirements for all possible parallel landing scenarios. In particular, the following property is being proved:

For all possible states s1, s2 and all possible trajectories and assuming that one of the airplanes is in its intended course at the time of the prediction, the algorithm modeled by the function chtrack will warn i seconds before a collision.

# 3.3 Scalable Processor-Independent Design for Electromagnetic Resilience (SPI-DER)

The Scalable Processor-Independent Design for Electromagnetic Resilience (SPIDER) project is a new project jointly sponsored by NASA and the FAA. The purpose of this project is to develop an advanced fault-tolerant computer system, gain understanding of the new RTCA DO-254 guidance document by developing SPIDER in accordance with its provisions, and generate training materials for the FAA. The RTCA DO-254 document entitled "Design Assurance Guidance for Airborne Electronic Hardware" is intended to provide a basis for the certification of complex electronic hardware devices used in future aircraft.

For the case study, a core subsystem of the Scalable Processor-Independent Design for Electromagnetic Resilience (SPIDER) has been selected. SPIDER is a new fault-tolerant architecture under development at NASA Langley Research Center. Several factors motivated the choice of a fault-tolerant system for this exercise. Hardware realizations of fault-tolerant protocols are generally compact designs; this allows for comprehensive treatment within the time constraints of a training exercise. Also, the behavior of fault-tolerant devices is inherently complex; such a device is clearly within the scope of DO-254. Furthermore, there is a considerable amount of research literature addressing the formal analysis of fault-tolerant protocols; a fault-tolerant system is a good candidate for a formal methods demonstration. Finally, any device expected to recover from transient failures will necessarily need to deal with a bounded set of permanent failures, as well.

In the SPIDER architecture, the primary basis for fault-tolerance is a communication subsystem called the Reliable Optical Bus (ROBUS). This concept builds on twenty years of fault-tolerant

computing research at NASA Langley Research Center<sup>2</sup>

The SPIDER architecture has been formally modeled and analyzed using a hybrid fault model (See section 4.2.11.) Faulty nodes are globally classified based on the locally observable characteristics to other nodes within the system. The system is partitioned into Fault Containment Regions (FCRs) that ensure independence of random physical failures. The failure status of an FCR is then one of four mutually exclusive possibilities: Good, Benign Faulty, Symmetric Faulty, and Asymmetric Faulty. As part of the conceptual design activities, the algorithms for providing the fault-tolerant services are being formally specified and verified using PVS (http://pvs.csl.sri.com/). The focus of the verification activities during the detailed design and implementation stages will be to preserve the integrity of the verification performed at the conceptual design level. We also intend to explore elemental analysis and safety-specific analysis as we proceed but nothing has been done with these techniques yet.

An initial lab prototype of the ROBUS has been developed using FPGAs and eight off-the-shelf PCs. The lab prototype does not have an operating system and is not packaged in EMI-resistant hardware. The fundamental fault-tolerance protocols (i.e. group membership, clock synchronization, interactive consistency) have been completed. The formal proofs are nearly complete<sup>3</sup>

# 3.4 Aviation Safety Program

The goal of the new NASA Aviation Safety Program is to reduce the civil aviation fatal accident rate by 80% in ten years and 90% in twenty years. In 2000, a competitive procurement (NRA 99-LaRC-4) resulted in 4 awards that apply formal methods to this goal.

- Rockwell Collins Advanced Technology Center: Develop extensions to existing methods and commercial off-the-shelf tools that enable (1) requirements modeling and analysis, (2) safety analysis and partitioning, (3) mode confusion detection, applying formal methods to many different portions of the life-cycle, such as (1) requirements analysis, (2) high-level design, (3) detailed design, and (4) implementation, and (4) auto-generation of code.

- Honeywell Engines and Systems: utilize new Time Triggered Architecture (TTA) developed in Europe for the automotive industry by TTTech and formal verification methods to develop a FTIMA architecture. Targeted application is Full Authority Digital Engine Control (FADEC). SRI International is performing a formal verification of the key protocols [133, 134].

- Barron Associates/Goodrich: Develop formal verification methods that can serve as a basis for certifying non-adaptive neural nets for use on military and commercial aircraft[70].

- University of Virginia/Litton: Identify causes and develop tools to facilitate integration of formal verification methods into the software development lifecycle within an aerospace company. Current focus is on developing a specification tool that integrates natural language and formal language in a synergistic manner.

See section 4.1.2 for previous research this program is building upon. This work is supported by the Flight Critical Systems Design and Validation component of the Aviation Safety Program (AvSP).

$<sup>^2</sup>$ The main concept was inspired by a fault-tolerant system designed as part of the Fly-by-Light/Power-by-Wire (FBL/PBW) program.

<sup>&</sup>lt;sup>3</sup>The proofs have been completed for earlier versions, but are being updated as nice improvements have been made to the protocols themselves.

# 3.5 Information Technology Strategic Research (ITSR)

The Information Technology Strategic Research (ITSR) program is being led by NASA Ames. The current work is centered around the development of a rigorous approach to verifying avionics computing platforms that support integrated modular avionics.

# 3.5.1 Integrated Modular Avionics

Two contracts are supporting this thrust:

- Honeywell DEOS Project: A cooperative agreement with Honeywell (SRI International as a subcontractor) is applying formal methods to DEOS, which is a partitioned real-time operating system used in Honeywell's Primus Epic flight deck that is being developed to DO-178B Level A certification standards.

- Open PVS Project: A contract with SRI International (with Honeywell as a subcontractor) to open up PVS internals to other domain-specific tools. This contract is also being used to extend PVS's capabilities and to directly support the DEOS project. See section 3.8.2 for details about this work.

The goal of the Honeywell/SRI DEOS project is to demonstrate that formal methods can be used to assure the safety of new operating systems being developed for commercial avionics that support Integrated Modular Avionics. Integrated Modular Avionics (IMA) is beginning to emerge in commercial aviation as a more cost-effective means for implementing advanced avionics systems (reducing size, weight, power and recurring cost). IMA systems use shared computing resources to simultaneously host functions of differing criticality in separate logical partitions. But the cost savings and increased flexibility comes with a significantly greater safety risk. The sharing of resources raises the possibility of a low criticality task adversely affecting a high-criticality task. Therefore, it is essential that rigorous methods of assurance be developed that can guarantee that operating systems that are providing logical partitions are indeed free of errors that could compromise the safety of critical applications. The verification technology developed under this task is being demonstrated on a new Honeywell commercial operating system called DEOS.

The developed formal methods technology has already been successfully demonstrated on an early version of DEOS [27]. However, as DEOS has continued to evolve it has become more

complex and the verification problem has become increasingly more difficult. Recently slack-time reclamation and reallocation has been added to DEOS, which has dramatically increased the size of the state-space of the formal models. The previous approach based upon model checking has not scaled up to this problem size. The Honeywell/SRI research team is currently seeking to develop a verification method based upon both model checking and theorem proving. The status of this project is available at [28].

For more information about the Open PVS project see section 3.8.2.

# 3.5.2 MC/DC Tutorial

In cooperation with Rockwell Collins Inc, the Boeing Company, and the FAA, a tutorial was developed for MC/DC structural coverage, which is mandated by the FAA software certification document DO-178B[62]. The tutorial provides a practical approach to assessing modified condition/decision coverage (MC/DC) for aviation software products that must comply with regulatory guidance for DO-178B level A software. The tutorial's approach to MC/DC is a 5-step process that allows a certification authority or verification analyst to evaluate MC/DC claims without the aid of a coverage tool. In addition to the MC/DC approach, the tutorial addresses factors to consider in selecting and qualifying a structural coverage analysis tool, tips for reviewing life cycle data related to MC/DC, and pitfalls common to structural coverage analysis.

# 3.5.3 Object Oriented Technology in Aviation

The Object Oriented Technology in Aviation (OOTiA) project is a joint effort with the FAA to develop guidelines for the safe use of object oriented technology in software development. Aviation software developers, like many software developers, are advocating the use of object-oriented technology (OOT) as a way to increase productivity and reusability of software. Unlike the mainstream software industry, however, OOT has not seen widespread use in commercial aviation applications. A primary reason is that the RTCA/DO-178B guide, Software Considerations in Airborne Systems and Equipment Certification, does not specifically address OOT. Consequently, certification authorities have relied on issue papers on a project-by-project basis to address OOT concerns.

Current work on the project includes a task with the Boeing Company to look at the impact of object orientation on structural coverage. Also, OOTiA workshops with the FAA and industry are being conducted to identify safety issues relevant to using OOT and to propose acceptable solutions. The goal is to produce general guidelines to help software developers meet DO-178B when using OOT; and also provide useful evaluation criteria for certification authorities. Information about the OOTiA project is available at http://shemesh.larc.nasa.gov/foot/

#### 3.5.4 PVS Strategies

One of the major obstacles to the transfer of formal methods technology to industrial practice has been the high manpower cost of developing proofs. Although the proof of a complex system property often involves difficult reasoning, the task is further encumbered in modern theorem proving tools by an insufficient automated support for manipulating nonlinear algebraic formulas. To overcome this problem a task was issued to the PVS developers to improve the capabilities of the PVS theorem prover in this area. Unfortunately the term-rewriting approach taken by the contractor did not completely resolve the problem. Consequently Dr. Ben Di Vito decided to address the problem in a new way. He recognized that there will always be a limit to where automation can carry you, so he decided to develop a suite of proof-manipulation commands that mimic the style

of proof used in high-school algebra. These commands raise the level of abstraction of the proof process and eliminate the need for the time-consuming search for lemmas in the PVS prelude. Dr. Di Vito also developed a new interface for prover command invocation. See [39] for details. See also 3.8.1 for related work.

# 3.6 Engineering For Complex Systems Program

The Engineering for Complex Systems (ECS) Program is part of NASA's Office of Aerospace Technology's Pioneer Revolutionary Technology program. The primary objective of the program is to develop new approaches to system engineering and design that will substantially reduce safety and success risks for NASA missions. We have three research projects under ECS:

- Causality Analysis Using Symbolic Expression (CAUSE)

- Formal-Enough Notations for Computer-system Engineering (FENCE)

- Formal Specifications Database

#### 3.6.1 CAUSE

The goal of CAUSE is to develop appropriate notations and tools for creating and analyzing arguments about causes of failures. We believe that fully understanding past failures is an essential precondition for mitigating safety and success risks when designing new systems. Some expected benefits from successful completion of the project include the following: (1) improved confidence in the correctness of explanations of the causes of failures; (2) increased use of lessons taught by previous failures for improving new designs; and (3) storing of causal explanations in a form suitable for automated search, retrieval, and analysis.

We are currently completing a detailed analysis of existing notations and techniques for causal analysis. Once this analysis is complete, we will begin building prototype tools for creating, displaying, analyzing, storing, and retrieving causal arguments[59].

#### 3.6.2 **FENCE**

The goal of the FENCE project is to develop techniques and tools for appropriate integration of natural, visual, and formal notations for requirements elicitation, capture, and tracing for software-intensive systems. The motivation for this work is to try to achieve the benefits of the different notations, while mitigating the problems of any specific one. The research approach being pursued is to develop techniques and tools to integrate requirements specifications developed in natural, graphical, and mathematical languages so that the resulting requirements will be (1) understandable by all who must understand them, (2) analyzable for completeness, consistency, and other desired attributes, and (3) traceable and verifiable throughout the system life-cycle. These tools and techniques are will be developed through cooperation among computer scientists, software engineers, system engineers, linguists, and application domain experts.

There are currently three main parts of the FENCE project:

- University of Virginia: Integrating Natural and Formal Languages

- Safeware: Spectrum-RL tools

- Mathworks: Formal Methods Applied to Simulink and Stateflow

#### **Integrating Natural and Formal Languages**

The University of Virginia is extending the work that they began under the Aviation Safety Program by further developing the necessary theories and tools to enable the effective integration of natural language and formal languages for system requirements specification. This research effort is one of the first in the world to try to apply important concepts from linguistics (such as cognitive categories, hierarchies, and economy) to the problems of computer system requirements elicitation and propagation [58].

The Zeus toolkit, which serves as the basis for the work, is available on the web at

http://www.cs.virginia.edu/zed/zeus/

#### SpecTRM-RL Development and Demonstration

Safeware Engineering Corporation is working to improve their requirements modeling and analysis tool named SpecTRM-RL in the following ways:

- Improvement of the human interface to make SpecTRM easily usable by industry with minimal training.

- Expanded visualizations (both static and dynamic) of SpecTRM models.

- Expand the static analysis capabilities of SpecTRM

- Demonstrate the usability of the tool by applying it to a realistic NASA-related system or subsystem.

#### Mathworks

SRI is seeking to develop formal methods to support the analysis of Stateflow diagrams. In principle one would like to model check the Stateflow diagrams which are at the heart of a Simulink design, but it is impossible to establish anything useful without some knowledge of the constraints imposed by the differential equations in the other blocks. The SRI approach is to automatically construct sound discrete abstractions of the differential equations using automated theorem proving over the reals. A new decision procedure called QEPCAD, which performs quantifier elimination using cylindrical algebraic decomposition is used to find the sign-invariant regions. The end result is a completely discrete system you can model check[153].

http://www.csl.sri.com/users/tiwari/hscc02.html

The constructed abstractions are conservative and can be used to establish safety properties of the original system. The technique works on linear and non-linear polynomial hybrid systems, that is, the guards on discrete transitions and the continuous flows in all modes can be specified using arbitrary polynomial expressions over the continuous variables. A prototype tool in the SAL environment has been developed which uses the PVS theorem prover. The technique appears to have a good potential to scale to large and complex hybrid systems.

#### 3.6.3 Formal Specifications Database

Despite steady progress in theorem proving tools, effective use of formal methods is still held back by a lack of codified deductive knowledge. Theorem proving today takes place too close to the ground, too close to first principles. Many of the potential benefits will lie dormant until engineers can reason at the level of their problem domains rather than elementary properties of mathematics.

The goal of the Formal Specifications Database task is to extend Langley's work on PVS libraries by developing a capability for compiling, structuring and hosting a database of deductive theories suitable for integration with leading formal methods tools. A large-scale infrastructure (10K theories, 1M theorems) will enhance productivity for interactive theorem prover users. Passive collaboration will be encouraged by enabling theory contributions from users worldwide.

A database server is being established based on the PostgreSQL DBMS. Web server interfaces are being developed using the Zope Web applications tools. A small amount of application software will need to run within the theorem provers, e.g., special strategies for PVS. Populating the database will be a large, gradual effort that will be continued through community contributions once the server is fully operational.

# 3.7 Timing Analysis by Model Checking

Odyssey Research Associates (now known as ATC-NY) has been awarded a three-year contract to develop analysis methods for real-time systems analysis. Timing aspects of embedded systems have been notoriously difficult to analyze and verify. This work will address some of the limitations of Rate Monotonic Analysis (RMA) by applying model checking, a technique with successful industrial applications in hardware design. In addition to schedulability, the new methods will be able to analyze such properties as freedom from deadlock and from certain timing-dependent runtime errors. The goal is both to increase the design space and to reduce the costs of verification. The new methods will be applied to a suitable avionics subsystem. The work concentrates on applying the methods to designs expressed in Abstract Ada, a modeling notation based on a runtime system that meets the Ravenscar Profile.

# 3.8 PVS Development

NASA Langley's formal methods program has exploited the capabilities of PVS (Practical Verification System) developed by SRI International

http://www.csl.sri.com/sri-csl-fm.html

in no small measure. We have found the tool to be extremely capable, but have also desired improvements. Consequently, over the past decade we have funded improvements and extensions to the PVS system. The application of this theorem prover to real industrial applications has pushed this technology in many ways. In [115], Sam Owre, et. al. describe how NASA's program has shaped the development of PVS. Several tutorial introductions to PVS are available [34, 10, 148, 15, 117, 147] some of which were written at Langley.

# 3.8.1 Langley Inhouse Contributions

The Langley inhouse team has been supporting the PVS theorem prover by developing libraries and strategies. Libraries are the main way for users to extend a theorem prover, and they are an excellent way to support reuse and reduce the cost of new applications.

The following table provides a brief summary of NASA Langley PVS libraries:

| array.dmp.gz         | min, max, majority, sort, concatenation over arrays + permutations         |  |  |

|----------------------|----------------------------------------------------------------------------|--|--|

| calculus.dmp.gz      | axiomatic version of calculus                                              |  |  |

| div.dmp.gz           | integer division: Ada and number theory definitions                        |  |  |

| mod.dmp.gz           | modulo arithmetic: $mod(i,j)$ : {k  $abs(k) < abs(j)$ } = $i-j*floor(i/j)$ |  |  |

| reals.dmp.gz         | summations, sup, inf, sqrt over the reals, abs lemmas                      |  |  |

| nat_funs.dmp.gz      | special functions over nats: min, max, mod, div                            |  |  |

| trig.dmp.gz          | trigonometry: definitions, identities, approximations                      |  |  |

| graphs.dmp.gz        | graph theory: connectedness, walks, trees, Menger's Theorem                |  |  |

| digraphs.dmp.gz      | directed graphs: circuits, maximal subtrees, paths, dags                   |  |  |

| number_theory.dmp.gz | fundamental theorem arithmetic, primes infinite cardinality                |  |  |

| bags.dmp.gz          | bags, finite bags, inductions, conversions to sets                         |  |  |

| analysis.dmp.gz      | real analysis, limits, continuity, derivatives                             |  |  |

| series.dmp.gz        | power series, comparison test, ratio test, Taylor's theorem                |  |  |

| powersets.dmp.gz     | powersets: bijections, cardinality                                         |  |  |

| fixedpoints.dmp.gz   | fixed-points of [set[T] -> set[T]], mu-calculus, dual(H)                   |  |  |

The following table provides a summary of the strategies developed at NASA Langley:

| Name         | Download             | Documentation     | Concept                            |

|--------------|----------------------|-------------------|------------------------------------|

| Munoz/Mayero | field-strategy       | README-field      | remove divisions from a formula    |

| Di Vito      | manip-package.tar.gz | manip.ps          | algebraic manipulation of formulas |

| Butler       | test-probs.dmp       | test-prob-doc.txt | theorem prover benchmark problems  |

These libraries and strategies are available at:

http://shemesh.larc.nasa.gov/fm/ftp/larc/PVS-library/pvslib.html

The Langley MANIP package assists users to develop proofs of arithmetic properties that require extensive use of built-in and new libraries. The FIELD package supports automatic proof of formulas involving division and nonlinear products.

# 3.8.2 Open PVS Contract

SRI international (with a subcontract with Honeywell HTC) has been awarded a three-year contract to develop a customizable version of PVS[114, 113, 144]. The goal of this work is provide a more customizable and more open system architecture for PVS; make decision procedures available standalone and demonstrate their utility on Honeywell Applications. such as the Honeywell HOPTs (Hierarchical Operational Procedure Tables) tool for analyzing mode transition tables.

During the first year of the contract, SRI integrated a SAT solver (i.e. propositional satisfiability) with their stand-alone ICS decision procedures, which advances the power of the automation for certain problems (e.g., bounded model checking). The result is that one can automatically solve enormous formulas with large, complex propositional structures. The idea is as follows. You have a huge formula with lots of propositional structure (thousands of if-then-elses, ands, implies etc.) and interpreted terms at the leaves (x + y < z etc). The basic idea is "variable abstraction", which replaces any interpreted term with a new propositional constant (e.g., Q replaces x + y < z). Then you try to find a satisfying assignment to the resulting propositional formula (i.e., it's now a SAT problem). The SAT solver might come up with a solution that requires Q to be true and some

other P to be false etc. and so you now take the interpretation of those terms and give them to the decision procedure to see if they are simultaneously valid. If so, you're done; if not, you ask the SAT solver to find a different solution. Now you know the previous assignment didn't work and you don't want the SAT solver to generate another similar one. But you've just applied the decision procedure to the result of the previous assignment and discovered it is false, so you do a bit of work to find pieces of that assignment that are inconsistent on their own (e.g., "Q and not P" might be). You then throw the negation of those into the set of facts that the SAT solver knows before you ask it for another solution. By being clever about how you do this (and by seeding the process with facts about all pairs and triples of terms, and by having as many "don't cares" as possible) you rapidly cut down the search space. What makes all this work is that the decision procedures are enormously fast, and so are the latest SAT solvers. The result is that we can now solve enormous formulas of this type<sup>4</sup>.

During the second year of the contract SRI focused on adding new capabilities to PVS that allow authors of specification libraries to control how the system and theorem prover use libraries. Capability was added to PVS to (1) indicate which formulas should automatically be used as rewrites and/or expanded during typechecking (macros), (2) control the application of conversions, and (3) allow user-defined proof strategies to be loaded with a library. These capabilities were implemented in PVS 2.4.1 released January 2002.

#### 3.8.3 Past Enhancements

NASA Langley has supported the development of abstract datatypes in PVS [118] and the formal semantics for the specification language [143]. In 1996 NASA Langley sponsored the development of a tabular notation for PVS[116]. NASA Langley also supported the development of the PVS validation suite and funded a task to develop an approach for efficient direct execution of PVS specifications that can help users validate their specification through exploration of its behavior on test cases or symbolic execution. With the 2.3 release of PVS, users "run" a specification as if were a program, many times faster than can be achieved using rewriting. Static analysis for live variables allows safe use of destructive updates so that compiled PVS runs at speeds comparable to an imperative program.

Recently NASA Langley funded SRI to develop a mechanization for theory interpretations. The developed mechanization will make it possible to show that one collection of theories is correctly interpreted by another collection of theories under a user-specified interpretation<sup>5</sup>.

#### 3.8.4 PVS Classes

The formal methods team has provided training classes on the PVS theorem prover every 2 to 3 years (1995, 1997, 1998, 2001). The course is designed to accommodate a small number of professionals (12-16) with engineering backgrounds and provides hands-on exercises that develop

<sup>&</sup>lt;sup>4</sup>Bounded model checking is currently the leading approach in model checking because it is more robust than BDDs and finds deeper bugs faster. Some researchers are trying to extend SAT solvers with some ability to do arithmetic (e.g., small-domain instantiations). The SRI approach is unique in that they extend their SAT solver with a sophisticated decision procedure.

<sup>&</sup>lt;sup>5</sup>The mechanization will generate the proof obligations necessary to ensure the appropriate relationship, and provide theorem-proving enhancements (for example, rewriting under congruences, and congruence closure) that enable these obligations to be discharged efficiently. The PVS grammar will been extended so that names can include mappings. The goal is to map uninterpreted types and constants of a source theory into types and constants, respectively, of another theory.

the skills presented in the lectures. There have been attendees from Rockwell Collins, Honeywell, Loral, Draper Labs, Rome AFB, JPL, and several Universities.

# 4 Past Efforts

This section describes previous work in three categories: technology transfer, fault-tolerant systems, other fundamental research.

#### 4.1 Fundamental Research

#### 4.1.1 Streamlining Software Aspects of Certification

Kelly Hayhurst served as the Technical Program Manager for a FAA initiative called Streamlining Software Aspects of Certification (SSAC) starting in November 1997. The goal of the SSAC program was to identify and eliminate unnecessary costs in software aspects of certification for both airborne and ground-based systems. Unnecessary costs in certification not only waste money, but they also can delay adopting new, safety-enhancing technologies.

Since January 1998, the SSAC team has conducted 3 industry workshops and 1 FAA workshop to identify specific software issues to be addressed by the program. The team also conducted a survey of U.S. companies about the extent and significance of the issues identified through the workshops. A report describing the results and recommendations was published and is available electronically. The FAA response to the survey recommendations and the letter accompanying this response are also available in PDF format.

In October 1999, the FAA discontinued funding for the SSAC team activities. However, there continues to be interest in the SSAC program results and recommendations. A presentation on the current status of the SSAC program was given at the FAA National Software Conference on April 20, 2000. See

```

http://shemesh.larc.nasa.gov/ssac/

```

to obtain details about these workshops and copies of the workshop reports. A published report [61] about the project is available electronically at

```

http://shemesh.larc.nasa.gov/ssac/workshop3.html

```

The FAA response to the survey recommendations and the letter accompanying this response are also available in PDF format at this web page.

# 4.1.2 Formal Methods Analysis of Mode Confusion

The January 30, 1995 issue of Aviation Week lists 184 incidents and accidents involving mode awareness including the Bangalore A320 crash (14 February 1990), the trasbourg A320 crash (20 January 1992), the Habsheim A320 crash (26 June 1988), and the Toulouse A330 crash (30 June 1994) [2]. These incidents and accidents reveal that pilots sometimes become confused about what the cockpit automation is doing. Consequently, human factors research is an obvious investment area. However, even a cursory look at the incident and accident data reveals that the mode confusion problem is much deeper than just training deficiencies and a lack of human-oriented design. This is readily acknowledged by human factors experts. For example, Charles E. Billings, writes in Aviation Automation: The Search for a Human-Centered Approach, 1997 (pg 144):

... today's flight management systems are "mode rich" and it is often difficult for pilots to keep track of them (see Fig 9.2). The second problem, which is related to the first involves lack of understanding by pilot's of the system's internal architecture and logic, and therefore a lack of understanding of what the machine is doing, and why, and what it is going to do next.

Similarly, Sarter and Woods write in Decomposing Automation (1994):

What is needed is better understanding of how the machine operates, not just how to operate the machine.

It seems that further progress in human factors will only come through a deeper scrutiny of the internals of the automation. Formal methods can contribute in this arena. The fundamental goal of formal methods is to capture requirements, designs, and implementations in a mathematically-based model that can be analyzed in a rigorous manner. By capturing the internal behavior of a flight deck in a rigorous and detailed formal model, the dark corners of a design can be analyzed.

This project is exploring two complementary strategies based on a formal model:

- Visualization: Create and display a clear, executable formal model of the automation that is easily understood by flight crew and use it to drive the flight deck simulation during training.

- Analysis: Conduct mathematical analysis of the model and search for mode confusion potential.

The first phase of a new project involving NASA Langley and Rockwell Collins in applying formal methods to a realistic business jet flight guidance system has been completed and was reported at DASC'98 [16]. A final report on the phase I work has been published[97].

#### 4.1.3 Formal Analysis of Avionics Partitioning

The RTCA Special Committee 182 (SC-182) was established to develop a Minimum Operational Performance Standard (MOPS) for an Avionics Computer Resource (ACR). The ACR will have the capability of performing multiple aircraft functions through use of partitioning. Fundamental to the success of the ACR strategy is a guarantee that the ACR platform will prevent any application from corrupting another. In particular, the ACR must provide:

- space partitioning (no matter what an application does it cannot corrupt the memory of another application), and

- time partitioning (no matter what an application does it cannot prevent another application from obtaining its scheduled allocation of CPU time)

#### while supporting:

- inter-partition communications, and

- common modular/configurable I/O (the ACR must allow the partitions access to external devices through a suite of bus protocols such as ARINC 429, ARINC 629, etc.)

Our first efforts have been directed towards developing an abstract formal model of space partitioning that can serve as the basis for evaluating the design of an ACR[154, 38]. The PVS formal model is based on mathematical modeling techniques developed by the computer security

community. The model has been used on three candidate designs, each an abstraction of features found in real systems.

SRI International was funded by the FAA and NASA to identify the requirements for partitioning in integrated modular avionics (IMA) and to explore how to achieve those requirements with very high assurance. The final report entitled "Partitioning in Avionics Architectures: Requirements, Mechanisms and Assurance" has been published [132].

# 4.1.4 Translating UML Into PVS

Odyssey Research Associates was tasked to develop a UML-based specification and analysis method appropriate for flight guidance systems. The goal was to develop a specification method that uses standard UML notation and develop algorithms to translate these specifications into PVS for analysis. ORA has defined a design style that is strictly hierarchical and local, declarative (i.e. not operational), and object oriented. The defined UML idiom uses restricted class/state diagrams and additional stereotypes for specification. ORA has defined the semantics of the UML subset formally. An executable definition generates formal PVS model of the UML design. The formal model respects the OO structure of the UML.

# 4.1.5 Previous ICASE Research

The Formal Methods research program at NASA Langley's Institute For Computer Applications in Science and Engineering (ICASE) has been developing and applying techniques and tools for the specification, analysis, and verification of aerospace digital systems. Research efforts focus especially on the investigation of heterogeneous verification technologies in order to enhance the utility of formal methods for specifying, analyzing, and verifying large-scale systems. Topics of investigation in the past included:

- applying state-exploration methods to the verification of flight-guidance systems and to the analysis of mode confusion [91, 51, 25]

- developing compositional approaches to Statecharts semantics (including UML Statecharts)[95, 92, 94]

- combining process algebras and temporal logics[26, 93]

#### 4.1.6 Efficient Validation of Superscalar Microprocessors

SRI has developed a new approach to decompose and incrementally build the proof of correctness of pipelined microprocessors. The approach centers around the construction of an abstraction function using *completion functions*, one per unfinished instruction in the pipeline. In addition to avoiding the term size and case explosion problem that limits the pure flushing approach, the new method helps localize errors and handles stages with iterative loops. A final report has been written and is under review to be published as a NASA CR [151].

#### 4.1.7 Specification of Floating-point Arithmetic

Significant portions of the ANSI/IEEE-854 [72] standard have been defined using the PVS [101] and HOL [20] systems. IEEE-854 is a standard for radix-independent floating-point arithmetic. The main motivating factors for the formalization of the standard are 1) The creation of a formal

specification against which an implementation (such as the AAMP5 [96]) could be verified; 2) The highly publicized floating-point divide flaw in the Intel Pentium (R) processor [138].

The formalization of the standard has brought to light the interesting and challenging issues of translating a natural language document into a logic based language in a precise, unambiguous, and accurate manner. In addition, the formalization of the standard in two different systems has given the opportunity to compare the verification systems and specification styles [24].

A parameterized formal theory of subtractive floating point division algorithms has been developed in the PVS specification language. This parameterized theory defines a general algorithm that covers a broad class of algorithms and can serve as a tool for design tradeoffs. This generalized theory has been formally proved to satisfy the IEEE-854 standard for floating point arithmetic. The proof covers the entire class of algorithms. Thus, after an optimal algorithm has been selected for a particular target technology, and the parameters are shown to be type-correct, one knows that your selected algorithm is formally consistent with the IEEE standard. This work was presented at the Formal Methods in Computer-Aided Design Conference (FMCAD) on Nov. 6-8, 1996 [104].

# 4.1.8 Hardware Verification Using Coinduction

This research was aimed at overcoming some of the technical problems associated with the formal verification of hardware. Often the initial value of state had to be retained in expression, even when they are no longer relevant. The formal models included the number of clock ticks since start of computation, which made it difficult to verify revisions to a design, particular for aggressive optimizations. Also the formal models restricted the design space available and verification was still expensive.

This work sought to overcome these limitations through use of a better formal model based upon stream equations. Hardware designs, which are represented as system of equations, can be refined using algebraic transformations. The state component represents the current state and not the initial state and there is no explicit clock parameter. There is also a significant potential for a much more efficient verification process. Stream equations lead to a corecursive definition of hardware behavior and hence allows verification by coinduction, a very efficient approach for verifying design optimizations. A general mechanized support for reasoning about streams (within theorem proving system PVS was developed and demonstrated on two significant case studies: (1) Fault-Tolerant Clock Synchronization Circuit [106, 103] and, (2) Floating Point Division[102].

#### 4.1.9 Formal Modeling of Dynamic Systems

Transition Assertions[21, 22] is an experimental modeling method to represent or specify real-time systems. The model is intended to be used where timing is a critical element. Timing constrains can be represented directly in the model and verified using mathematical logic. Variables and conditions in a system are functions from time to value. A system is specified by using transition templates which describe a cause and effect relation of the system. Each transition template consists of a durational lower and upper bound, enabling predicate, and execution predicate. Ten generic transition templates have been created featuring single transition, multiple transition, transition with preemption, transition with inertia, and a combination of these.

# 4.2 Early Technology Transfer Projects

# 4.2.1 AAMP5/AAMP-FV Project

In 1993, NASA Langley initiated a joint project involving Collins Commercial Avionics and SRI International. The goal was to investigate the application of formal techniques to a commercial microprocessor design, the Collins AAMP5 microprocessor. The AAMP5 is the latest member of the CAPS/AAMP family of microprocessors and is object code compatible with the AAMP2 processor [3]. The CAPS/AAMP family of microprocessors has been widely used by the commercial and military aerospace industries. Some examples of use of earlier members of the family (1) Boeing 747-400 IDS, (2) Boeing 737-300 EFIS, and (3) Boeing 757,767 AFDS

The first phase of the project consisted of the formal specification of the AAMP5 instruction set and microarchitecture using SRI's PVS. While formally specifying the microprocessor, two design errors were discovered in the microcode. These errors were uncovered as a result of questions raised by the formal methods researchers at Collins and SRI while seeking to formally specify the behavior of the microprocessor[96, 152]. The Collins formal methods team believes that this effort has prevented two significant errors from going into the first fabrication of the microprocessor.

The second phase of the project consisted of formally verifying the microcode of a representative subset of the AAMP5 instructions. Collins seeded two errors in the microcode provided to SRI in an attempt to assess the effectiveness of formal verification. Both of these errors (and suggested corrections) were discovered while proving the microcode correct[96]. It is noteworthy that both the level 2 and level 3 applications of formal methods were successful in finding bugs. Based on the success of the AAMP5 project, a new effort was initiated with Rockwell-Collins to apply formal methods in the design level verification of a microprocessor, currently designated as AAMP-FV. This project is nearing completion.

This work has has significant impact on the development of a hardware verification capability within PVS [36]. This project has also had major impact on Rockwell Collins. There are now four engineers at Collins that are skilled in formal methods. In the fall of 1996 Rockwell Collins hired a formal methods expert whose full-time job is to integrate the use of formal methods into their product lines.

Rockwell Collins used the formal specifications of the AAMP5/AAMP-FV micro-architecture as a means to design and perform prototype testing on their JEM1 Java chip. Collins was the first supplier to SUN Microsystems to deliver a microprocessor that directly executes the JAVA instruction set.

#### 4.2.2 Tablewise Project

Under NASA funding, Odyssey Research Associates worked with Honeywell Air Transport Systems Division (Phoenix) beginning in 1993 to study the incorporation of formal methods into the company's software development processes. As part of this work, ORA developed a prototype tool, called TableWise, to analyze the characteristics of certain types of operational procedure tables[67, 66]. Boeing Defense and Space Systems funded ORA to develop an extension to Tablewise: to enable it to reason about arithmetic expressions that are commonplace in navigation system decision logic at Boeing.

# 4.2.3 Space Shuttle Change Requests

A team spread across three NASA centers (LaRC, JSC, and JPL), together with support from Loral Space Information Systems <sup>6</sup>, SRI International, and VíGYAN Inc., was formed to study the application and technology transfer of formal methods to NASA space programs from 1992 until 1996. The NASA Formal Methods Demonstration Project for Space Applications focused on the use of formal methods for requirements analysis because the team believed that formal methods are more practically applied to requirements analysis than to late-lifecycle development phases [73]. This proved to be a valuable decision.

In 1993 a formal specification of a very mature piece of the Space Shuttle flight control requirements called Jet Select was developed. Few proofs were produced for the first specification, but 46 issues were identified and several minor errors were found in the requirements. A second specification was produced for an abstract (i.e., high level) representation of the Jet Select requirements. This abstraction, along with the 24 proofs of key properties, was accomplished in under 2 work months, and although it only uncovered 6 issues, several of these issues were significant [31].

NASA Langley's primary role in 1994–95 included support for three Space Shuttle software change requests (CRs)[32]. One CR concerned the integration of new Global Positioning System (GPS) functions[44, 37]., while a second CR concerned a new function to control contingency aborts known as Three Engine Out (3E/O)[33], and the third CR concerned improved crew displays when entering the "heading alignment cylinder" (HAC) during landing [123].

In addition to the Shuttle activities, LaRC contributed to two NASA guidebooks produced by the inter-center team. The first volume of the guidebook, published in 1995, is intended for managers of NASA projects who will be using formal methods in requirements analysis activities [110]. The second volume was published in 1997 and was aimed at practitioners [111]. LaRC's efforts in 1996 were directed primarily at this second guidebook volume, with members of the LaRC team having been the lead contributors.

#### 4.2.4 Boeing Hardware Devices

The Boeing Company was contracted by NASA Langley to develop advanced validation and verification techniques for fly-by-wire systems. As part of the project, Boeing explored the use of formal methods. The goal of this work was two-fold: (1) technology transfer of formal methods to Boeing, and (2) assessment of formal methods technology maturity.

The first phase of this project focused on the formal verification of "real" hardware devices using the HOL hardware verification methodology. With the assistance of a subcontract with U. C. Davis, Boeing partially verified a set of hardware devices, including a microprocessor[159], a floating-point coprocessor similar to the Intel 8087 but smaller[120, 119], a direct memory access (DMA) controller similar to the Intel 8237A but smaller[79], and a set of memory-management units[142, 139]. U. C. Davis also developed the generic-interpreter theory to aid in the formal specification and verification of hardware devices[160, 158, 157], and a horizontal-integration theory for composing verified devices into a system[141, 140, 121, 78]. After demonstrating the feasibility of verifying standard hardware devices, Boeing applied the methodology to a proprietary hardware device called the Processor Interface Unit (PIU) that was developed for aeronautics and space applications[48].

Boeing and U.C. Davis also performed an assessment of the U.K. Royal Signals and Radar Establishment's (RSRE) VIPER chip [86]. This was part of a now-completed 3 year Memorandum

<sup>&</sup>lt;sup>6</sup>now Lockheed Martin Space Information Systems

of Understanding (MOU) with RSRE. CLI and Langley researchers also performed assessments of the VIPER project[9, 23, 17].

#### 4.2.5 Verification of Existing Ada Applications Software

Odyssey Research Associates completed two tasks applying their Ada verification tools to aerospace applications. The first task was to verify some utility routines obtained from the NASA Goddard Space Flight Center and the NASA Lewis Research Center using their Ada Verification Tool named Penelope [55]. This task was accomplished in two steps: (1) formal specification of the routines and (2) formal verification of the routines. Both steps uncovered errors [47]. The second task was to formally specify the mode-control panel logic of a Boeing 737 experimental aircraft system using Larch (the specification language used by Penelope) [56].

#### 4.2.6 Asynchronous Communication

CLI developed a formal model of asynchronous communication and demonstrated its utility by formally verifying a widely used protocol for asynchronous communication called the bi-phase mark protocol, also known as "Bi- $\Phi$ -M," "FM" or "single density" [107]. It is one of several protocols implemented by microcontrollers such as the Intel 82530 and is used in the Intel 82C501AD Ethernet Serial Interface.

#### 4.2.7 Digital Design Derivation

Funded in part by a NASA Langley Graduate Student Research Program fellowship, Bhaskar Bose developed the Digital Design Derivation system (DDD) and used it to design a verified microprocessor. DDD implements a formal design algebra that allows a designer to transform a formal specification into a correct implementation[7]. Bose formally derived the DDD-FM9001[8] microprocessor from Hunt's top-level specification of the FM9001 microprocessor[71].

# 4.2.8 NASA Small Business Innovative Research Program

Through the NASA Small Business Innovative Research (SBIR) program we funded four formal methods proposals. We have funded three proposals through Phase II. The following list shows the year of selection, proposal title, and company funded.

- 1. 1998, Multi-Formal Hardware Verification System, Levetate Design Systems, Inc. (http://www.levetate.com/)

- 2. 1997, Verified VHDL Synthesizable Cores, Derivation Systems Inc. (http://www.derivation.com/)

- 3. 1994, Analysis Tools for VHSIC Hardware Description Language, Odyssey Research Associates, Inc. ( http://www.oracorp.com/ )

- 4. 1994, Digital Design Derivation System for Hardware Synthesis, Derivation Systems, Inc. (http://www.derivation.com/)

#### 4.2.9 Union Switch and Signal

As part of a joint research agreement, NASA Langley formal methods researchers collaborated with engineers at Union Switch and Signal (US&S) to use formal methods in the design of railway switching and control applications. Railway switching control systems, like digital flight control systems, are safety critical systems. US&S is the leading U.S. supplier of railway switching control systems.

The result of this first project was a formal mathematical model of a railway switching network, defined in two levels. The top level provided the mechanisms for defining the basic concepts: track, switches, trains and their positions and control liners of a train The second level formalized the standard railroad control method called the block model control system. A level 2 proof that the fixed block control system is "safe" with respect to the top level model was also completed [68]

The research team also looked at safety issues associated with a CAD system begin developed by US&S for use by railway control engineers. An area of particular concern has been the correctness of internal compilation processes which translate graphical representations of control diagrams into code that will be executed on US&S's proprietary V\_FRAME<sup>++</sup> architecture.

#### 4.2.10 CSDL Scoreboard Hardware

A joint project between ORA and Charles Stark Draper Laboratory (CSDL) was completed in 1993. NASA Langley and the Army had funded CSDL to build advanced, fault-tolerant computer systems for over two decades. During this time, CSDL became interested in the use of formal methods to increase confidence in their designs. ORA was given the task of formally specifying and verifying a key circuit (called the scoreboard) of the Fault-Tolerant Parallel Processor (FTPP) [60] in Clio [150]. The formal verification uncovered previously unknown design errors. When the scoreboard chip was fabricated, it worked without any error manifestation. It was the first time that CSDL produced a chip that worked "perfectly" on a first fabrication. CSDL credits VHDL-development tools and formal methods for the success.

#### 4.2.11 Allied Signal's Hybrid Fault Algorithms

Thambidurai and Park (Allied-Signal) introduced a hybrid fault model (1988) that classified faults into three categories: asymmetric, symmetric and crash. They further suggested the need for and developed an algorithm that had capabilities beyond that of the earlier Byzantine generals algorithms. In particular, their algorithm can mask the effects of a less severe class of faults, in a more effective way<sup>7</sup>. A formal analysis by SRI discovered flaws in Allied-Signal's algorithm Z and together with Allied Signal, they developed an improved algorithm [88, 87, 89].

The newly developed hybrid-fault theory was then applied to the analysis of the Charles Stark Draper Labs "Fault-Tolerant Processor" (FTP). A unique feature of this architecture is its use of "interstages" to relay messages between processors. These are significantly smaller than a processor and lead to an asymmetric architecture that is far more efficient than the traditional Byzantine agreement architectures<sup>8</sup>. The SRI work not only formalized the existing informal analysis but extended it to cover a wider range of faulty behavior[90]. Also, SRI generalized their clock synchronization work to encompass the hybrid fault model [128].

<sup>&</sup>lt;sup>7</sup>This was done during the development of the [Multicomputer Architecture for Fault Tolerance (MAFT) system [155].

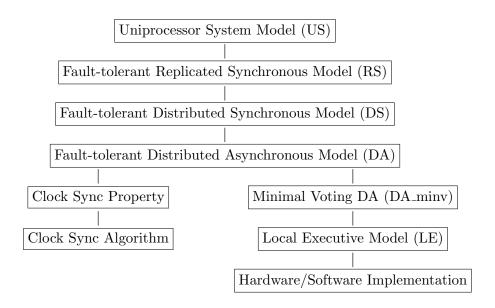

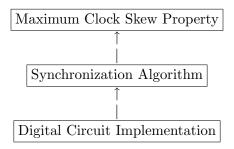

<sup>&</sup>lt;sup>8</sup>This combination of algorithm, architecture, and fault model represents the best known compromise between economy and fault tolerance. Other combinations either tolerate less faults, or less severe kinds of faults, for a given level of redundancy, or require more hardware to tolerate the same number and kinds of faults.