# SimCheck : An Expressive Type-system for Simulink <sup>1</sup>

### Pritam Roy<sup>1</sup> Natarajan Shankar<sup>2</sup>

University of California, Los Angeles<sup>1</sup> SRI International<sup>2</sup>

April 14, 2010

<sup>1</sup>supported by NSF Grant CSR-EHCS(CPS)-0834810 and NASA Cooperative Agreement NNX08AY53A

Pritam Roy, N. Shankar

SimCheck : An Expressive Type-system for Simulink

Introduction

Model Translation to Yices Type Annotation and Checking Property Verification Conclusion

#### Model Translation to Yices

- Type Annotation and Checking

- Property Verification

#### Conclusion

Pritam Roy, N. Shankar SimCheck : An Expressive Type-system for Simulink

ヘロト ヘ回ト ヘヨト ヘヨト

Simulink as a Model Type Checking

# Simulink as Modeling Tool

- Matlab/Simulink is very popular modeling language in the industry

- Language of choice to design a complex embedded or control system

- Easy to draw lines and boxes drag and drop

- A comprehensive set of function blocks

ヘロト ヘ回ト ヘヨト ヘヨト

Simulink as a Model Type Checking

# Simulink as Modeling Tool

- Matlab/Simulink is very popular modeling language in the industry

- Language of choice to design a complex embedded or control system

- Easy to draw lines and boxes drag and drop

- A comprehensive set of function blocks

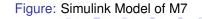

Figure: M7 Surgical Robot Arm

Pritam Roy, N. Shankar

SimCheck : An Expressive Type-system for Simulink

Simulink as a Model Type Checking

# **Simulink Semantics**

- A Simulink model is represented graphically by means of a number of interconnected blocks.

- Lines between blocks connect block outputs to block inputs and represent data flow signals.

- Blocks can be built from a large number of predefined library blocks, which can be nested in an arbitrary manner,

A D b 4 A b

э

Simulink as a Model Type Checking

### **Simulink Semantics**

- Blocks may have states, which may consist of a discrete-time and a continuous-time part.

- The output of a block is computed by an output function, based on its input and its current state and time.

- An update function calculates the next discrete state.

イロト 不得 トイヨト イヨト 三連

Simulink as a Model Type Checking

# Why Type Checking is Important ?

- type of a variable provide an abstraction of the data values the variable can store

- type checking : process of verifying and enforcing the constraints of types

- expressive type-checking catches most of the bugs eagerly (avoid crashing during execution)

イロト イポト イヨト イヨト 一座

Simulink as a Model Type Checking

# Types in Simulink

- basic types are Bool, signed and unsigned integer types, tuples, vectors and matrices, and strings.

- Default type is double

- Ports in a block and connectors have types.

< < >> < </>

→ Ξ → < Ξ →</p>

Simulink as a Model Type Checking

# Types in Simulink

- basic types are Bool, signed and unsigned integer types, tuples, vectors and matrices, and strings.

- Default type is double

- Ports in a block and connectors have types.

- has a limited capability for checking type correctness.

- no systematic design-by-contract capability for Simulink.

< 🗇 >

.⊒...>

Simulink as a Model Type Checking

### What we need?

We need a capability that uses contracts to carry out

- Type inference for basic types,

- Annotate links with expressive types (over values, dimensions and units of physical variables)

- Generate test cases,

- Capture interfaces and behaviors,

- Monitor type conformance, and

- Verify type correctness relative to such expressive types

イロト イポト イヨト イヨト 一座

Simulink as a Model Type Checking

### What we need?

We need a capability that uses contracts to carry out

- Type inference for basic types,

- Annotate links with expressive types (over values, dimensions and units of physical variables)

- Generate test cases,

- Capture interfaces and behaviors,

- Monitor type conformance, and

- Verify type correctness relative to such expressive types

The SimCheck type system/tool can be used to specify and verify these requirements.

イロト イポト イヨト イヨト 一座

Introduction

Model Translation to Yices Type Annotation and Checking Property Verification Conclusion

Simulink as a Model Type Checking

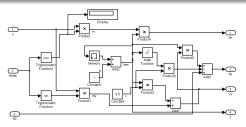

# SimCheck Framework

- The whole package is built in Matlab language.

- integrated the type checker/verifier inside the Matlab environment editing customization file

- Simulink files have mdl extensions

- Used simulink APIs to obtain the parameters of blocks and connectors

くロト (過) (目) (日)

Outline

#### 2 Model Translation to Yices

Type Annotation and Checking

Property Verification

#### Conclusion

Pritam Roy, N. Shankar SimCheck : An Expressive Type-system for Simulink

ヘロト ヘ回ト ヘヨト ヘヨト

Yices MDL2YICES

# Yices - SMT Solvers

- SMT is the problem of determining satisfiability of formulas modulo background theories (e.g. linear arithmetic, arrays, data types, bit vectors etc.)

- Yices is an SMT Solver developed at SRI International.

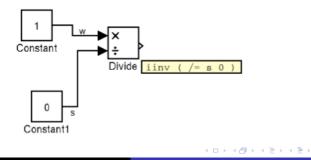

- The input language of the Yices language in the semantics of a divide block:

```

(define Divide :: (-> real real real ))

(define DivideIn1 :: real )

(define DivideIn2 :: ( subtype (n :: real ) (/= n 0)))

(define DivideOut :: real )

(assert (= DivideOut ( Divide DivideIn1 DivideIn2 )))

```

<ロ> <同> <同> < 回> < 回> < 回> < 回> < 回> < 回</p>

Yices MDL2YICES

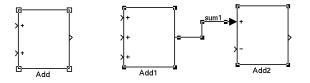

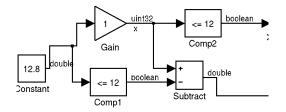

### **Basic Blocks**

For example, Constant block is translated as

(define ConstantOutltime1 :: real )

(assert (= ConstantOutltime1 1))

イロト イポト イヨト イヨト 一座

Yices MDL2YICES

### **Basic Blocks**

#### For example, Constant block is translated as

(define ConstantOut1time1 :: real )

(assert (= ConstantOut1time1 1))

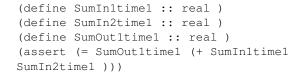

#### Sum block is translated as

<ロ> <同> <同> < 回> < 回> < 回> < 回> < 回> < 回</p>

Yices MDL2YICES

# Memory Blocks

Memory with initial value 70 can be translated to two consecutive clock cycles as follows:

イロト 不得 トイヨト イヨト 三連

Outline

Model Translation to Yices

Type Annotation and Checking

Property Verification

#### Conclusion

Pritam Roy, N. Shankar SimCheck : An Expressive Type-system for Simulink

ヘロト ヘ回ト ヘヨト ヘヨト

User Given Types Unit Checking Expressive Type Systems Compatibility Checking Test-case Generation

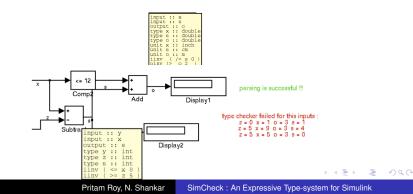

# **User Given Types**

- User can annotate the type constraints or constraints on the signals

- Constraints can be written on the blocks or globally

| input : | x         |

|---------|-----------|

| input : | s         |

| output  | :: 0      |

| type x  | :: double |

| type s  | :: double |

| type o  | :: double |

| unit x  | :: inch   |

| unit s  | : cm      |

| unit o  | : m       |

| iinv (  | /= s 0 )  |

| oinv (> | 02)       |

ヨトメヨト

User Given Types Unit Checking Expressive Type Systems Compatibility Checking Test-case Generation

# **Unit Checking**

For an adder with inputs signals x and s and output o, we obtain

|                                         | (define | dist(x) ::       | int)         |          |         |

|-----------------------------------------|---------|------------------|--------------|----------|---------|

| input :: x<br>input :: s<br>output :: o | (define | dist(s) ::       | int)         |          |         |

|                                         | (define | dist(o) ::       | int)         |          |         |

| type x :: double<br>type s :: double    | (define | x:: real)        |              |          |         |

| type o :: double                        | (define | s:: real)        |              |          |         |

| unit x :: inch<br>unit s :: cm          | (define | o:: real)        |              |          |         |

| unit o :: m<br>iinv (/= s 0)            | (assert | (= dist(x)       | dist(s)))    |          |         |

| oinv (> 0 2 )                           | (assert | (= dist(x)       | dist(o)))    |          |         |

|                                         | (assert | $(= \circ (+ (*$ | 254/10000 x) | (* 1/100 | ) s)))) |

イロト イポト イヨト イヨト 三連

User Given Types Unit Checking Expressive Type Systems Compatibility Checking Test-case Generation

# Unit Checking

Pritam Roy, N. Shankar SimCheck : An Expressive Type-system for Simulink

-20

User Given Types Unit Checking Expressive Type Systems Compatibility Checking Test-case Generation

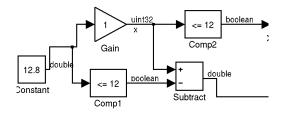

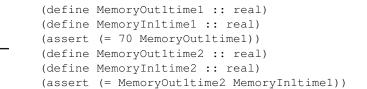

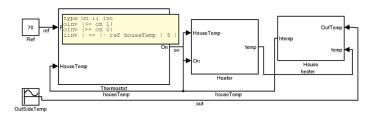

# Dependent Types and Refinement Types

- Refinement types : capture constraints on the signals to a function e.g. odd integer, non-zero divisor

- Dependent types : capture dependency between input ports or output port and input ports

Figure: Thermostat Example with Dependent and RefinementTypes

ヘロト ヘアト ヘビト ヘビト

User Given Types Unit Checking Expressive Type Systems Compatibility Checking Test-case Generation

# Typechecking Incompatibility

- Two components may have different input assumptions and output guarantees

- May not work together

- If SMT solver returns UNSAT then there is no environment

User Given Types Unit Checking Expressive Type Systems Compatibility Checking Test-case Generation

# Test Case Generation

- For each signal *s* and constraint Ps(s), we want to show that  $\neg Ps(s) \land \land_{r \neq s} Pr(r)$ .

- Yices solver returns either a negative answer (unsat) or a positive answer with a satisfying variable assignment.

Conclusion

ヘロト ヘ回ト ヘヨト ヘヨト

# **Property Verification**

#### **Bounded Model Checking**

- 1. transition(1, k + 1) = dump2yices(model, vBlocks, k)

- $2. \quad \psi = \vee_{d \in \{1,2,\dots,k+1\}} \neg \phi_d$

- 3. check-sat(transition, $\psi$ )

イロト 不得 トイヨト イヨト 三連

# **Property Verification**

#### **Bounded Model Checking**

- 1. transition(1, k + 1) = dump2yices(model, vBlocks, k)

- $2. \quad \psi = \vee_{d \in \{1,2,\dots,k+1\}} \neg \phi_d$

- 3. check-sat(transition, $\psi$ )

#### K-induction

- 1. transition(1, k + 1) = dump2yices(model, vBlocks, k)

- 2.  $\psi = (\wedge_{d \in \{1,2,\ldots,k\}} \phi_d) \wedge \neg \phi_{k+1}$

- 3. check-sat (transition,  $\psi$ )

イロト 不得 トイヨト イヨト 三連

Related Work Future Directions Conclusions

### Outline

#### Introduction

Type Annotation and Checking

ヘロト ヘ回ト ヘヨト ヘヨト

Related Work Future Directions Conclusions

### **Related Tools**

- Reactis : test generation and simulation of test cases including embedded C code.

- Mathworks SDV : test generation and prove and refute functional properties.

- CheckMate : analysis of properties of hybrid systems using a finite state abstraction of the dynamics.

イロト イポト イヨト イヨト 一座

Related Work Future Directions Conclusions

# **Related Tools**

- HiLiTE : use of static analysis of input range for generation of test-cases, detection of ambiguities and divide-by-zero errors, robustness, and unreachable code.

- Simulink-to-Lustre : translation for type inference on Simulink models and the resulting Lustre output can be analyzed using model checkers.

- Gryphon : a number of tools, including model checkers, for analysis of Simulink/Stateflow models.

- kind : bounded model checking, k-induction

イロト 不得 トイヨト イヨト 三連

Related Work Future Directions Conclusions

### **Future Directions**

- Interface types to capture temporal input-output behavior of Stateflow

- Map the bounded integers to their fixed-point representations or bit vectors.

- Reason about Matlab functions blocks via static analysis

- Cover other properties such as the robustness, error bounds for floating point computations,

- Verification of model/code correspondence through the use of test cases

- Translate Simulink models to SAL and HybridSAL for symbolic analysis

イロト イポト イヨト イヨト 一座

Related Work Future Directions Conclusions

### Conclusions

- Type system capture constraints, dimensions and units of signals, and the relationships between signals.

- Annotations expressed in the constraint language of Yices

- Proof obligations translated to constraint solver

- Obligations used to check compatibility w.r.t. dimensions, generate counterexamples and test cases, and to prove type correctness.

- Yices performs BMC and *k*-induction to refute or verify type invariants.

- Eventual goal is to use this capability to certify the correctness of such systems and monitor type conformance

イロト 不得 トイヨト イヨト 三連

Related Work Future Directions Conclusions

#### Thank You

Pritam Roy, N. Shankar SimCheck : An Expressive Type-system for Simulink

◆□> ◆□> ◆豆> ◆豆> ・豆 ・ のへで