NASA Conference Publication 10176

#### Third NASA Langley Formal Methods Workshop

Compiled by C. Michael Holloway Langley Research Center • Hampton, Virginia

(NASA-CP-10176)THIRD NASA LANGLEYN96-10026FORMAL METHODS WORKSHOP(NASA.--THRU--Langley Research Center)239 pN96-10037UnclasUnclas--

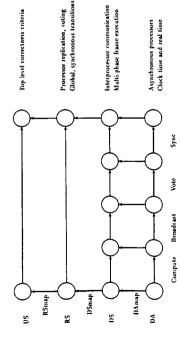

G3/59 0059510

Proceedings of a workshop sponsored by the National Aeronautics and Space Administration, Washington, D.C., and held at Langley Research Center, Hampton, Virginia May 10–12, 1995

#### TABLE OF CONTENTS

| Introduction                                                                                                                                                                                                                                                                                               | 3                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Final Agenda                                                                                                                                                                                                                                                                                               | 5 -0                            |

|                                                                                                                                                                                                                                                                                                            | 11 -0<br>13-0<br>15 -6<br>25 -6 |

| Overview of NASA Langley's Formal Methods Program, Ricky W. Butler                                                                                                                                                                                                                                         | 53 -0                           |

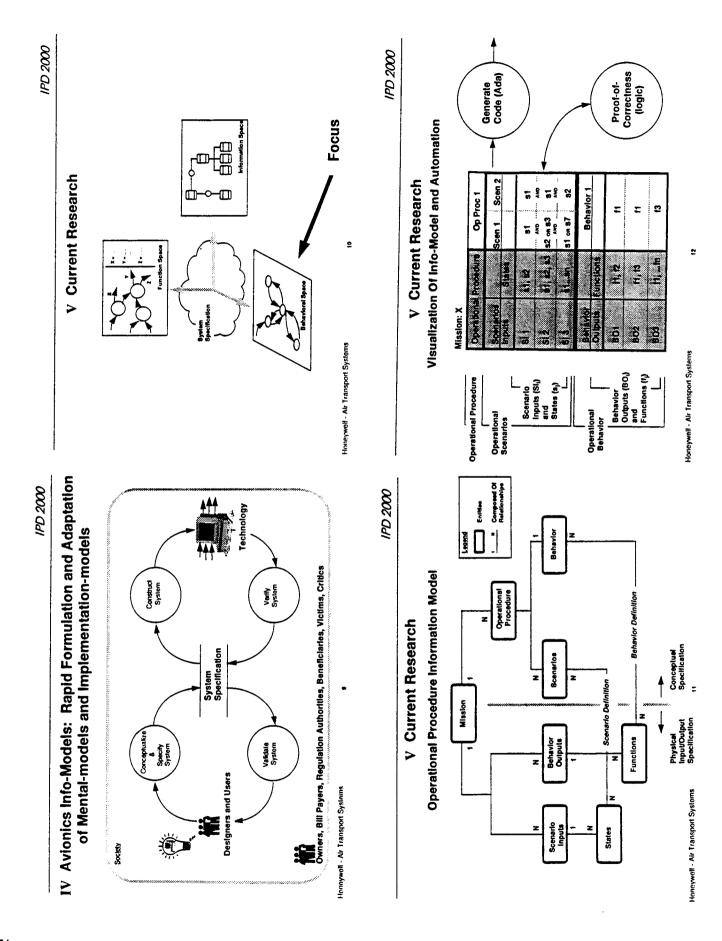

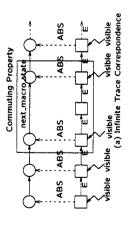

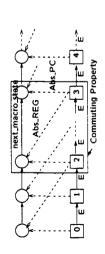

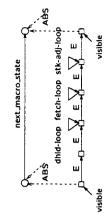

| <ul> <li>Session 2: LaRC-sponsored Industrial Applications</li> <li>The AAMP5/AAMP-FV Project, Steve Miller</li> <li>Union Switch &amp; Signal Project, Joe Profeta and Doug Hoover</li> <li>Honeywell Software Development Project, Lance Sherry and Doug Hoover</li> </ul>                               | 59 <sup>/</sup><br>65~          |

|                                                                                                                                                                                                                                                                                                            |                                 |

| <ul> <li>Session 3: Industry Perspectives on Formal Methods</li> <li>Session 4: Software Systems (1)</li> <li>Formal Verification for Fault-Tolerant Architectures/PVS Design, John Rushby</li> <li>Formal Methods Demonstration Project for Space Applications, John Kelly<br/>and Ben DiVito.</li> </ul> | . 89>                           |

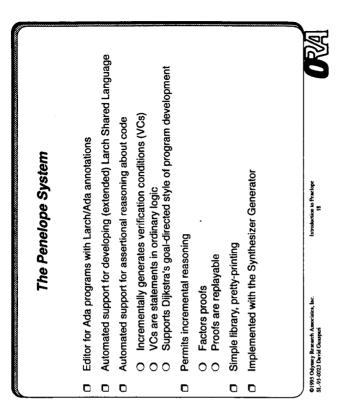

| <ul> <li>Session 5: Software Systems (2)</li> <li>Ada 9X Language Precision Team, David Guaspari</li> <li>Introduction to Penelope and Its Applications, David Guaspari</li> </ul>                                                                                                                         |                                 |

| <ul> <li>Session 6: Hardware Systems</li></ul>                                                                                                                                                                                                                                                             | 141-5<br>1490m / T              |

| Session 7: Researcher Perspectives on Formal Methods                                                                                                                                                                                                                                                       | 165 - crri                      |

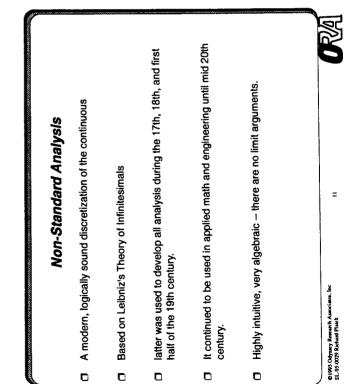

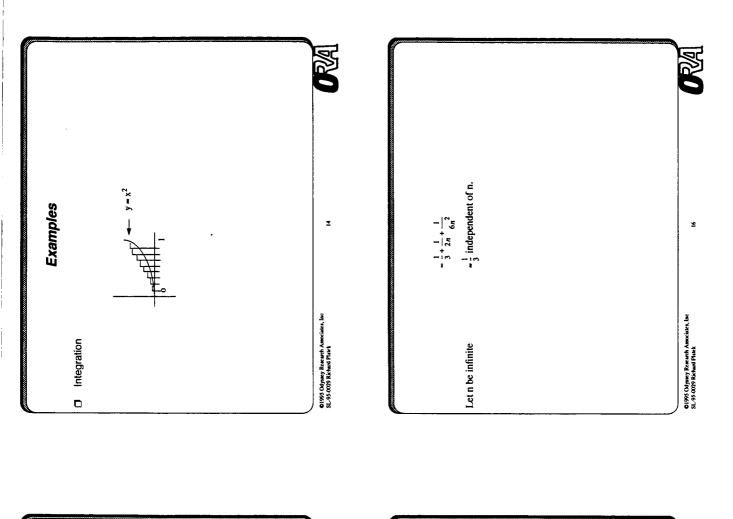

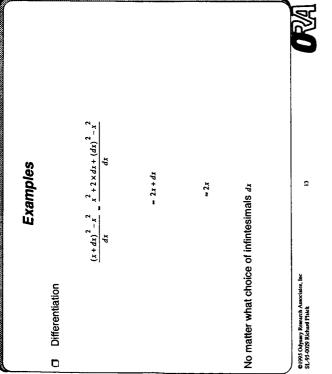

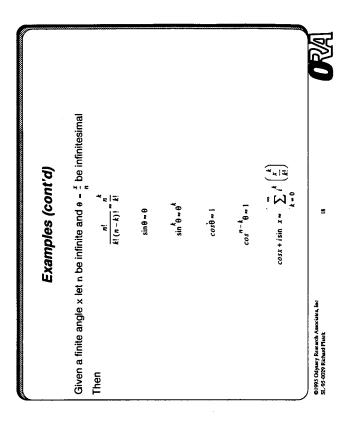

| <ul> <li>Session 8: Research Issues (1)</li> <li>Safety Analysis, John Knight.</li> <li>Non-standard Analysis and Embedded Software, Richard Platek</li> </ul>                                                                                                                                             | 173-7                           |

| <ul> <li>Session 9: Research Issues (2)</li> <li>Hybrid Fault Algorithms, Pat Lincoln</li> <li>Model Checking, David Dill</li> </ul>                                                                                                                                                                       | 191ーマ<br>193ーロ<br>211ータ         |

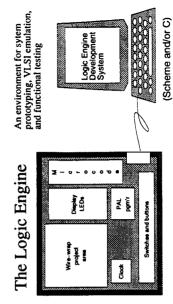

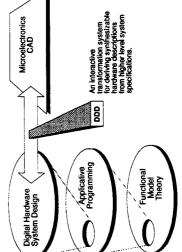

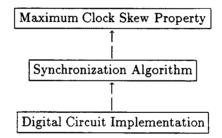

| <ul> <li>Session 10: Research Issues (3)</li> <li>The DDD Scheme Machine, Steve Johnson</li> <li>Formal Development of a Clock Synchronization Circuit, Paul Miner</li> </ul>                                                                                                                              | 219-10                          |

| Appendix A: List of Attendees                                                                                                                                                                                                                                                                              | 233                             |

| Appendix B: Comments from Attendees                                                                                                                                                                                                                                                                        | 243                             |

| Appendix C: Overview of NASA Langley's Formal Methods Program                                                                                                                                                                                                                                              | 245                             |

#### INTRODUCTION

On May 10-12, 1995, the formal methods team at the NASA Langley Research Center sponsored their third workshop<sup>1</sup> on the application of formal methods to the design and verification of life-critical systems. This workshop brought together formal methods researchers, industry engineers, and academicians to discuss the potential of NASA-sponsored formal methods and to investigate new opportunities for applying these methods to industry problems.

This publication constitutes the proceedings of the workshop. It contains copies of the material presented at the workshop, summaries of many of the presentations, a complete list of attendees, and a detailed summary of the Langley formal methods program. Much of the material contained herein is available electronically through the World-Wide Web via the following URL: http://atb-www.larc.nasa.gov/WS95/proceedings.html.

On behalf of the formal methods team, we thank all of the presenters and attendees for their contributions to making this workshop a great success. We look forward to seeing all of you again at our next workshop.

C. Michael Holloway, Workshop Co-chairman Ricky W. Butler, Workshop Co-chairman

<sup>&</sup>lt;sup>1</sup> Previous workshops were held in 1990 (see NASA Conference Publication 10052) and 1992 (see NASA Conference Publication 10110).

#### **Final Agenda**

PRECEDING PAGE BLANK NOT FILMED

#### Third NASA Langley

#### Formal Methods Workshop

NASA Langley

#### May 10-12, 1995 H. J. E. Reid Conference Center NASA Langley Research Center Hampton, Virginia

Sponsored by Formal Methods Team Assessment Technology Branch Information & Electromagnetic Technology Division Research and Technology Group

Proceedings available on the World-WideWeb at http://atb-www.larc.nasa.gov/WS95/proceedings.html

#### Wednesday, May 10, 1995

| 8:00 – 8:45   | Late Registration                                                                                                                           |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|               | Session 1: Introduction to Formal Methods<br>Chaired by Ricky Butler                                                                        |

| 8:45 - 9:00   | Welcome<br>Milton Holt, Chief, Information & Electromagnetic Technology Division                                                            |

| 9:00 – 9:30   | Rationale for Formal Methods<br>Ricky Butler, NASA Langley Research Center                                                                  |

| 9:30 - 10:30  | An Informal Introduction to Formal Methods<br>Michael Holloway, Ricky Butler, and Paul Miner<br>NASA Langley Research Center                |

| 10:30 – 11:00 | Break                                                                                                                                       |

| 11:00 – 12:00 | An Informal Introduction to Formal Methods (continued)                                                                                      |

| 12:00 – 12:30 | Overview of NASA Langley's Formal Methods Program<br>Ricky Butler, NASA Langley Research Center                                             |

| 12:30 – 1:30  | Lunch in NASA Cafeteria                                                                                                                     |

|               | Session 2: LaRC-sponsored Industrial Applications<br>Chaired by Ricky Butler                                                                |

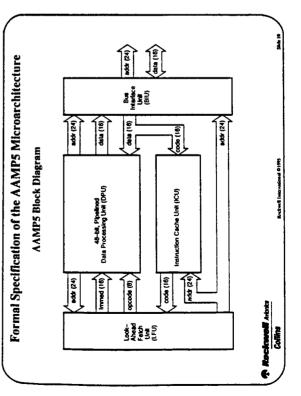

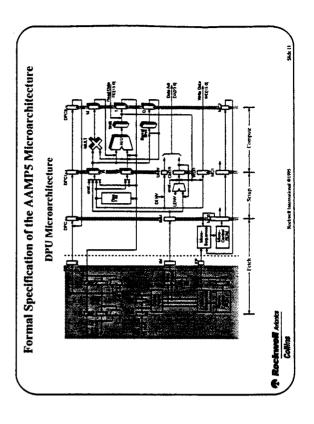

| 1:30 – 2:00   | The AAMP5/AAMP-FV Project<br>Steve Miller, Rockwell-Collins<br>Mandayam Srivas, SRI International                                           |

| 2:00 - 2:30   | Union Switch & Signal Project<br>Joe Profeta, Union Switch & Signal<br>Doug Hoover, Odyssey Research Associates                             |

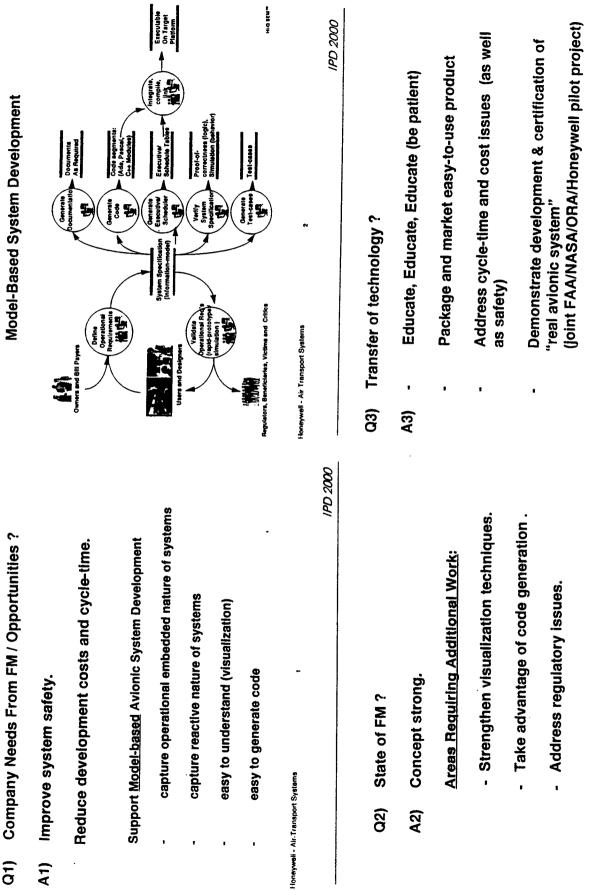

| 2:30 – 3:00   | Honeywell Software Development Project<br>Lance Sherry, Honeywell<br>Doug Hoover, Odyssey Research Associates                               |

| 3:00 - 3:30   | Break                                                                                                                                       |

|               | Session 3: Industry Perspectives on Formal Methods<br>Chaired by Michael Holloway                                                           |

| 3:30 – 5:00   | Panel Session<br>Scott French, Loral ATC<br>Steve Miller, Rockwell-Collins<br>Joe Profeta, Union Switch & Signal<br>Lance Sherry, Honeywell |

| 5:00 - 6:00   | Cash Bar Social in Reid Conference Center                                                                                                   |

#### Thursday, May 11, 1995

|       |     |      | Session 4: Software Systems (1)<br>Chaired by Ricky Butler                                                                                                                |

|-------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8:30  | -   | 9:30 | Formal Verification for Fault-Tolerant Architectures/PVS Design<br>John Rushby, SRI International                                                                         |

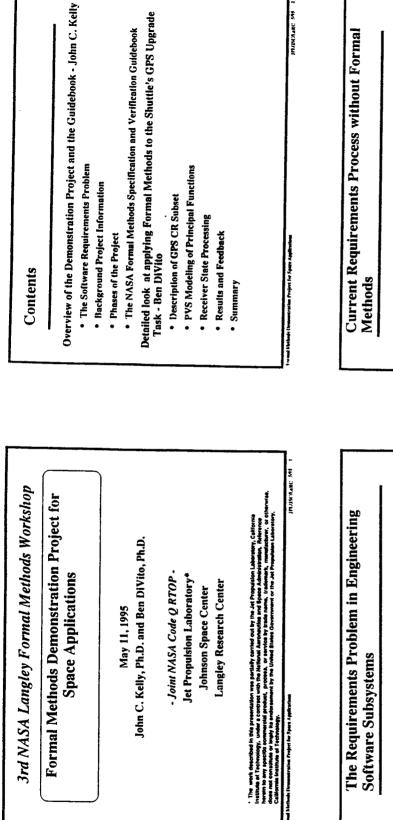

| 9:30  | - 1 | 0:30 | Formal Methods Demonstration Project for Space Applications<br>Ben DiVito, VÍGYAN, Inc.<br>John Kelly, Jet Propulsion Laboratory                                          |

| 10:30 | - 1 | 0:45 | Break                                                                                                                                                                     |

|       |     |      | Session 5: Software Systems (2)<br>Chaired by Michael Holloway                                                                                                            |

| 10:45 | - 1 | 1:45 | Ada 9X Language Precision Team<br>David Guaspari, Odyssey Research Associates                                                                                             |

| 11:45 | - 1 | 2:30 | Introduction to Penelope and Its Applications<br>David Guaspari, Odyssey Research Associates                                                                              |

| 12:30 | -   | 1:30 | Lunch in NASA Cafeteria                                                                                                                                                   |

|       |     |      | Session 6: Hardware Systems<br>Chaired by Paul Miner                                                                                                                      |

| 1:30  | -   | 2:00 | The Formal Verification Technology Used on AAMP5<br>Mandayam Srivas, SRI International                                                                                    |

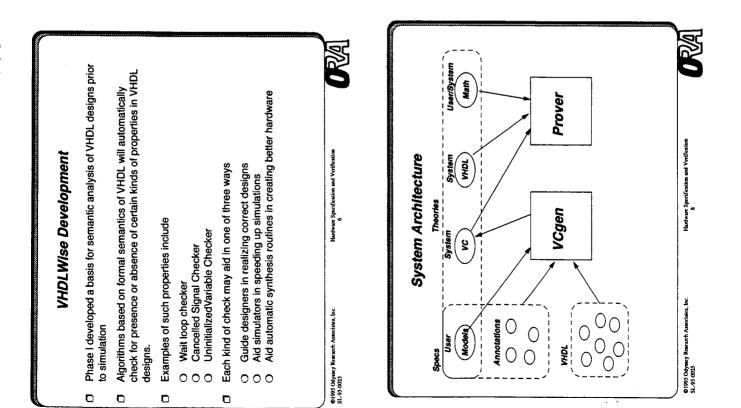

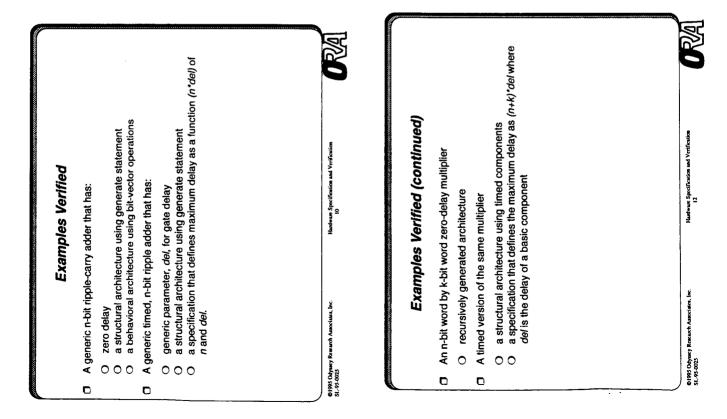

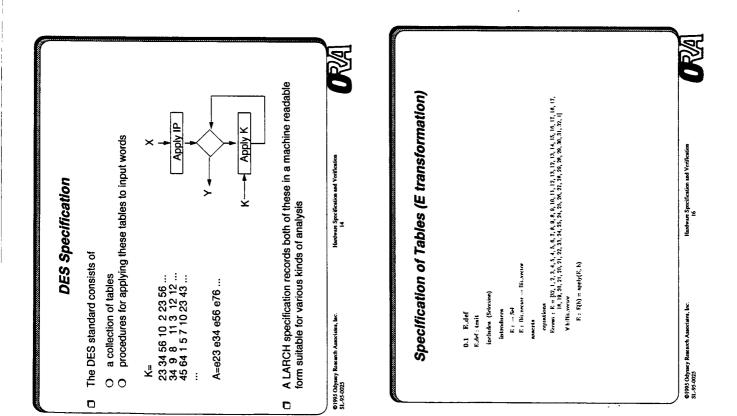

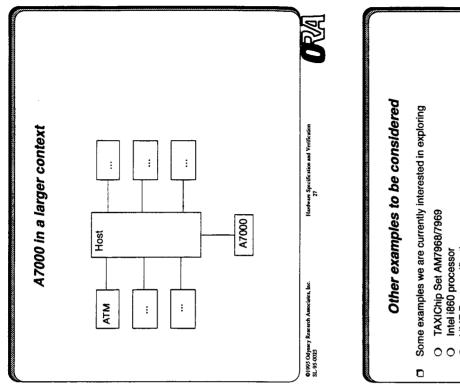

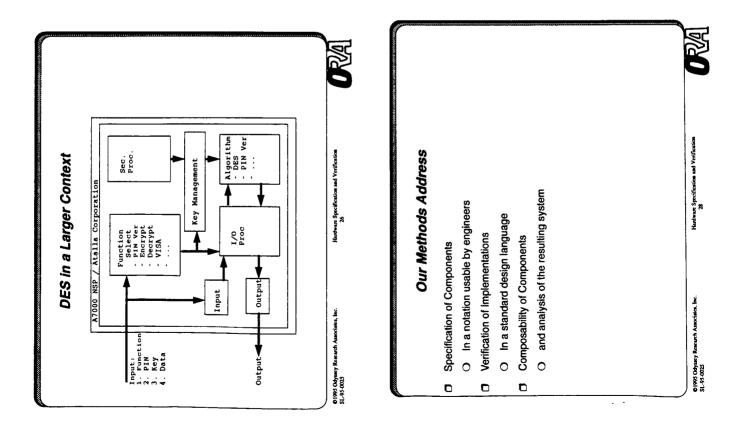

| 2:00  | -   | 2:30 | Specification and Verification of VHDL Designs<br>Damir Jamsek, Odyssey Research Associates                                                                               |

| 2:30  | - : | 3:15 | Derivational Reasoning System<br>Bhaskar Bose, Derivation Systems Inc.                                                                                                    |

| 3:15  | -   | 3:30 | Break                                                                                                                                                                     |

|       |     |      | Session 7: Researcher Perspectives on Formal Methods<br>Chaired by Jim Caldwell                                                                                           |

| 3:30  | -   | 5:00 | Panel Session<br>David Dill, Stanford University<br>Doug Hoover, Odyssey Research Associates<br>Steve Johnson, Indiana University<br>Natarajan Shankar, SRI International |

| 6:30  | -   | 8:00 | Dinner at Captain George's Seafood Restaurant                                                                                                                             |

in the second se

#### Friday, May 12, 1995

|               | Session 8: Research Issues (1)<br>Chaired by Michael Holloway                                     |

|---------------|---------------------------------------------------------------------------------------------------|

| 8:30 - 9:15   | Safety Analysis<br>John Knight, University of Virginia                                            |

| 9:15 – 10:00  | Non-standard Analysis and Software<br>Richard Platek, Odyssey Research Associates                 |

| 10:00 - 10:30 | Break                                                                                             |

|               | Session 9: Research Issues (2)<br>Chaired by Victor Carreño                                       |

| 10:30 – 11:15 | Hybrid Fault Algorithms<br>Pat Lincoln, SRI International                                         |

| 11:15 – 12:00 | Model Checking<br>David Dill, Stanford University                                                 |

| 12:00 – 1:30  | Lunch in NASA Cafeteria                                                                           |

|               | Session 10: Research Issues (3)<br>Chaired by Ricky Butler                                        |

| 1:30 – 2:00   | The DDD Scheme Machine<br>Steve Johnson, Indiana University                                       |

| 2:00 – 2:30   | Formal Development of a Clock Synchronization Circuit<br>Paul Miner, NASA Langley Research Center |

| 2:30 – 2:40   | Closing Remarks<br>Ricky Butler, NASA Langley Research Center                                     |

#### **Session 1: Introduction to Formal Methods**

Ricky W. Butler, Chair

• Welcome, by H. Milton Holt, Chief, Information & Electromagnetic Technology Division

\* Rationale for Formal Methods, by Ricky W. Butler

• An Informal Introduction to Formal Methods, by C. Michael Holloway, Paul S. Miner, and Ricky W. Butler

• Overview of NASA Langley's Formal Methods Program, by Ricky W. Butler

TO ESTABLISH IN COOPERATION WITH U.S. INDUSTRY, TECHNOLOGICAL PRECEDENTS IN SELECTED INFORMATION AND ELECTROMAGNETIC SYSTEMS AREAS. SYSTEM TO TRANSFER BENEFICIAL ELEMENTS OF THIS RESEARCH WITHIN NASA AND TO U.S. INDUSTRY AND OTHER-GOVERNMENT AGENDIES TO CONDUCT THIRD-GENERATION RESEARCH FOCUSED ON NATIONAL NEEDS AT ALL LEVELS OF INFORMATION AND ELECTROMAGNETIC SYSTEM TECHNOLOGIES. LaRC TECHNOLOGY OPTIONS/ TRANSFER THEORY MISSION SYSTEM INTEGRATION 1 ASSESSMENT RIG L Ì

PRECEDING PAGE BLANK NOT FILMED PAGE 12 INTENTIONALLY DLANK

Ricky W. Butler

NASA Langley Research Center

May 10, 1995

1. The Problem

2. Why Formal Methods Is Needed (i.e. Why Standard Practice Won't Work)

3. What is Formal Methods

A Small Sample of Notorious Design Errors

14

PAGE

Saturation of AT&T metwork on 15 January 1990 caused by a timing problem in a fault-recovery mechanism.

Failure to launch STS-1 (synchronization of backup computer)

• Therac 25 medical radiation-treatment machine responsible for the death of two people.

• Loss of data from Voyager at Jupiter (loss of clock sync)

• Patriot failure at Dharan (clock drift)

INTENTIONALLY BLANK

• In flight tests of the X31, the control system went into a reversionary mode four times in the first nine flights usually due to a disagreement between the two air data sources.

• AFTI-F16-Asynchronous operation, skew, and sensor noise led each channel to declare others failed in flight test 44. Flown home on a single channel. Other potentially disastrous bugs detected in flight tests 15 and 36. • X29 bug detected by simulation after 162 "at-risk" flights. Analysis showed that the bug could have led to instability and consequent loss-of-aircraft.

Pentium floating point division bug

Software Systems Are Unpredictable and Unreliable

Gibbs, W. Wayt: "Software's Chronic Crisis", Scientific American, Sept. 1994, pp. 86-95.

Studies have shown that for every six new large-scale software systems that are put into operation, two others are cancelled. The average software development project overshoots its schedule by half; larger projects generally do worse. And three quarters of all large systems are "operating failures" that either do not function as intended or are not used at all.

Despite 50 years of progress, the software industry remains years-perhaps decades-short of the mature engineering discipline needed to meet the demands of an information-age society

Software Systems Are Unpredictable and Unreliable (cont.)

Wiener, Lauren Ruth Digital Woes: Why We Should Not Depend Upon Software

Software products—even programs of modest size—are among the most complex artifacts that humans produce, and software development projects are among our most complex undertakings. They soak up however much time or money, however many people we throw at them.

The results are only modestly reliable. Even after the most thorough and rigorous testing some bugs remain. We can never test all threads through the system with all possible inputs.

Hardware Designs Are Unpredictable and Unreliable

Intel's President, Andy Grove, on comp.sys.intel Internet bulletin board:

After almost 25 years in the microprocessor business, I have come to the conclusion that no microprocessor is ever perfect; they just come closer to perfection with each stepping. In the life of a typical microprocessor, we go thru [sic] half a dozen or more such steppings....

# Michael Schrage, Washington Post Article (Dec 16, 1994)

Pentium type problems will prove to be the rule—rather than the isolated, aberrant exceptions—as new generations of complex hardware and software hit the market. More insidious errors and harmful bugs are inevitable. That is the new reality.

On the brink?

ŝ

Commercial aviation has an excellent safety record BUT

- There are some signs that we are near the threshold where traditional approaches will no longer be able to deliver safe systems.

- The industry is rapidly adopting more and more complicated software systems, e.g. Integrated Modular Avionics (SC-182).

A340 Incident (Near Heathrow on September 19, 1994)

- The commander's EFIS<sup>1</sup> map display symbology froze and lost all computed data [..].

- His MDCU<sup>2</sup> displayed the message 'PLEASE WAIT' and a *preflight* data load page. He was unable to obtain any other display.

- At roughly the same time, the copilot's EFIS and MCDU exhibited identical behavior.

- They 'dialed in' the ILS<sup>3</sup> using a back-up method,

- Then discovered they had some 2000 kgs of fuel less than expected (an erroneous indication).

- The autopilot's attempt to follow the glidepath resulted in unusually high pitch rates and so the autopilot was disconnected.

- The commander informed the tower they were having problems with the glideslope and requested an SRA (Surveillance Radar Approach)

- They landed without further incident; after taxiing in and shutting down, the fuel indications recovered.

<sup>1</sup>Electronic Flight Instrument System <sup>2</sup>Multi-function Control and Display Unit <sup>2</sup>Instrument Landing System

| ŝ   |

|-----|

| 03  |

| ā   |

| iag |

| σ   |

| ₽,  |

| 7   |

| 1   |

The reason for the wrong response of the autopilot and one flight director to the left turn demand was a *software crive* ... This error was known to Airbus Industrie and corrective measures for this and several other software deficiencies ... have been issued ...

### Post-flight analysis:

- The BITE data dump showed that the No 2 FMGEC had detected a CLASS 1 HARD failure within itself and a simultaneous fault within FMGEC No 1, but no hardware fault could be found.

- Airbus Industrie was aware of the double FMGS failure mode which had first emerged on the A320 series aircraft.

- According to Airbus Industrie, there are several ways in which the exchange of data and/or a problem in one computer can affect the other computer.

- Airbus Industrie has succeeded in radically reducing the frequency of double FMGS failures on the A320 series aircraft; they are also addressing the problem on the A330 and A340 series. [...]

"Air Accidents Investigation Branch of the UK Ministry of Thansportation

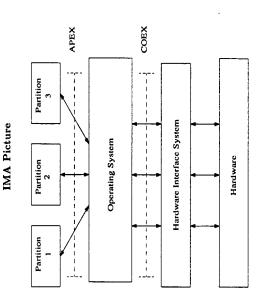

Radical Change In Digital Avionics for Commerical Aircraft

- Digital systems for commerical aircraft about to undergo a radical change

- The fundamental architecture of the avionics systems will move from "federated" to "integrated":

- <u>federated</u>: Each aircraft function resides on its own computer. Aircraft functions are certified.

- integrated: There is a shared computing resource on which multiple functions execute.

2

# The Motivation for this Change

According to ARINC 651, this approach [i.e. Integrated Modular Avionics (IMA)] will:

Reduce life-cycle cost through

- Reduced weight, power, and EE bay volume

- Reduced unscheduled maintenance, reduced spares and increase parts commonality

- Reduce first cost and cost of service life support through

- Reduced development, certification and production costs

- Reduced avionics weight and increased payload volume

Flexibility to efficiently meet customer requirements and im-

- riexibility to efficiently meet customer requirements and plement improvements

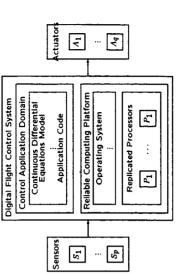

| • Task partitioning becomes life-critical.<br>IMA needs formal methods technology | to manage complexity However, the FAA has not developed<br>any supportable criteria for establishing a partition. Although<br>partitioning has been part of the certifications of the Gulf-<br>stream 4, Airbus A320, Boeing 747-400, Douglas MD-11 and<br>is being used extensively in the certification of the Boeing 777<br>and the ongoing certification of the 412CF helicopter, <i>the assur-</i><br><i>tance of the common has here non standardized and suce hered here here and the base non standardized and suce hered here base non standardized and suce hered here base non standardized and suce hered hered here as a standardized and suce hered here</i> | project almed at applying Formal Methods to the partitioning prob-<br>lem:<br>RTCA D0-178B recognizes partitioning as a crucial element<br>to manage complexity However, the FAA has not developed<br>any supportable criteria for establishing a partition. Although<br>partitioning has been part of the certifications of the Gulf-<br>stream 4, Airbus A320, Boeing 747-400, Douglas MD-11 and<br>is being used extensively in the certification of the Boeing 777<br>and the ongoing certification of the duce and<br>once of the commont has been non standardized and use lowely housed<br>parts of the commont has been and the and and use lowely housed |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| e<br>E                                                                            | unce of unce approvation was seen non sumartuized and was largely asso<br>on individual engineering judgement. There is a critical need to establish<br>supportable criteria for approving partitioning in avionics applications.<br><sup>14</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | indurated and was largely oused<br>here is a critical need to establish<br>ioning in avionics applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Why is Digital Design (SW and HW) so Hard to get Right?                           | Classical vs. Computer Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | uter Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| • There's nothing to go wrong but the design                                      | Classical Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Computer Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| • Our intuition and experience is with continuous systems—but in                  | continuous state space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | discrete state space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| digital system's the behavior is discontinuous                                    | smooth transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | abrupt transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| • Have to separately reason about or test millions of sequences of                | finite testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | finite testing inadequate,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| discrete state transitions                                                        | and interpolation OK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | interpolation unsound                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                   | build to withstand additional stress build to specific assumptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | build to specific assumptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| • Complexity exceeds our (unaided) intellectual grasp                             | mathematical modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | prototyping and testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

15

IMA Issues

FAA Interest

ł

.

Ì

Ì

i

ļ

i

| Three Basic Approaches to Overcoming the Design<br>Error Problem | <ul> <li>Testing (Lots of it)</li> <li>Design Diversity (i.e. Software Fault-Tolerance: N-version programming, recovery blocks, etc.)</li> <li>Fault Avoidance:</li> </ul> | - Formal Specification/Verification | – Automatic Program Synthesis<br>– Reusable Modules | 8 | Design Diversity (i.e. Software Fault Tolerance) | • Use different versions of a program developed by dif-<br>ferent teams.                    | • Vote the outputs of the different versions. | • Hope that the redundant programs will fail independently or nearly so. |                                                |  |

|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------|---|--------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------|--|

| Why Formal Methods is Needed:                                    |                                                                                                                                                                            |                                     |                                                     | 5 | Life Testing                                     | Basic Observation:<br>10 <sup>-9</sup> probability of failure estimate for a 1 hour mission | Requires                                      | $> 10^9$ hours of testing                                                | $(10^9 \text{ hours} = 114,000 \text{ years})$ |  |

| Can We Assume Independence for Multi-version Software?             | • Unlike physical failures governed by the laws of physics, software errors are the products of human reasoning. | <ul> <li>Subjective arguments have been offered for and against<br/>the independence assumption.</li> </ul> | • Subjective arguments for independence are not com-<br>pelling enough to assume it as an axiom.                                                                             | 2  | A More General Coincident Error Model? | Validating a general coincident error model would require<br>more time than life testing a single system:               | <ul> <li>Coincident errors must be observed</li> </ul> | <ul> <li>Coincident errors be shown to correspond to the general model</li> <li>Extremely rare coincident errors must be observed to show model applies in ultra-reliable region</li> </ul> | CONCLUSION:                                                   | For ultrareliable software, experiments cannot<br>demonstrate that a general coincident error model is<br>accurate. |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| What Enables Ultra-Reliability Quantification For Physical Failure | 10-9                                                                                                             |                                                                                                             | • The only thing that enables quantification of ultra-<br>reliability for hardware systems with respect to physi-<br>cal failure is the:<br><i>INDEPENDENCE ASSUMPTION</i> . | 12 | Independence Model                     | Experiments on Low Reliability Software (Kunght and Leveson)<br>• 27 versions of a program subjected to 1,000,000 input | cases.                                                 | • Observed average failure rate per input was 0.0007.                                                                                                                                       | • Independence model was rejected at 99% confidence<br>level. | • Other researchers have confirmed Knight-Leveson re-<br>sult.                                                      |

FM Versus Traditional Engineering of Digital Systems

| Method            | Approach                                                                                     | Confidence |

|-------------------|----------------------------------------------------------------------------------------------|------------|

| traditional       | Build according to engineering judge- Empirical<br>ment, test and measure failure rate       | Empirical  |

| formal<br>methods | Design according to fundamental Rational principles (axoms) and use deduction for refinement | Rational   |

Although testing methods will be used in conjunction with formal methods the *primary confidence* in this system is *not* derived from the empirical data.

52

26

**Digital System Modeling and Prediction**

- One way to predict behavior of a system is to construct a mathematical model and calculate it.

- For this to be effective, the model must be reasonably accurate and the calculations must be performed without error.

- For many continuous systems of traditional engineering, well-developed mathematical theories (e.g., Navier-Stokes equations for aerodynamics) are available.

- For computer systems, we must use discrete mathematics (logic, set theory) and build our own theories. Proofs of theorems take the place of numerical calculation.

# This is the essence of formal methods.

What is Formal Methods

Formal Methods

- Formal Specification: Use of notations derived from formal logic to describe

- assumptions about the world in which a system will operate

- requirements that the system is to achieve

- a design to accomplish those requirements

Formal Verification: Use of methods from formal logic to

- analyze specifications for certain forms of consistency, completeness

- prove that the design will satisfy the requirements, given the assumptions

- prove that a more detailed design implements a more abstract one

| Formal Methods: Specification                                                                                                                                                                                                                                                                                                                                                                                                                                        | Formal Methods: Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Instead of differential equations, the properties and behaviors are described using concepts from discrete mathematics: sets, graphs, partial orders, finite-state machines, and so on.</li> <li>The specification may be in traditional mathematical notation or in a computer-processable language: <ul> <li>enables typechecking</li> <li>some automatic consistency checks</li> </ul> </li> <li>Provides a clear, unambiguous specification.</li> </ul> | <ul> <li>Formal Verification is more akin to proving theorems in geometry than to ordinary numerical calculation,</li> <li>but like calculation it is performed according to strict rules</li> <li>so one person can check the work of another</li> <li>and computers can be used to automate some of the steps.</li> <li>The particular importance of formal methods to safety-critical systems is that they uniquely permit analysis of all the logical behaviors of a digital system [subject to some caveats].</li> <li>Total exploration is the only way to provide assurance that catastrophic failure does not lie hidden among the vast number of possible behaviors.</li> </ul> |

| R                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| How Is Total Exploration Possible?                                                                                                                                                                                                                                                                                                                                                                                                                                   | The Advantages of Formal Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Mathematical logic provides ways to reason about the properties of<br>large or infinite collections of related things in a finite manner:<br>• <i>skolemization</i> allows us to draw conclusions for all values of a given<br>variable by reasoning about a single representative symbolic con-                                                                                                                                                                     | • Enable faults in assumptions, requirements, design to be detected<br>earlier than otherwise due to greater precision and explicitness<br>early in the lifecycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • Enable faults to be detected with greater certainty than otherwise,<br>by augmenting reviews with analysis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| of some ordered domain (e.g., the natural numbers, 0, 1, 2, ) by<br>showing                                                                                                                                                                                                                                                                                                                                                                                          | • Can provide total coverage of selected, modeled properties.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (a) that the property is true for the least element (e.g., 0)<br>(b) that when it is true for all members up to some point (e.g., n),<br>then it is also true for the next point<br>(e.g., $n + 1$ )                                                                                                                                                                                                                                                                 | • Guarantee absence of specified faults (subject to accuracy of mod-<br>eling employed), because the calculations (proofs) can be checked<br>mechanically (by a theorem prover)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

31

Conclusions

- 1. Formal methods offers the most intellectually defensible means of producing life-critical systems

- 2. Formal methods is the application of mathematical logic to digital system design and verification

g

.

| <section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><text></text></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>Here presentations are <u>not</u> intended to</li> <li>These presentations are <u>not</u> intended to</li> <li>These presentations are <u>not</u> intended to</li> <li>Frable you to carry on a meaningful conversation with mathematical logicians</li> <li>Present a balanced view of the relative capabilities of existing formal methods tools and techniques</li> <li>Discuss all of the domains in which formal methods may be applied</li> <li>Discuss all of the domains in which formal methods may be applied</li> <li>Tell you all you need to know to become a formal methods expent</li> <li>Put you to steep</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><text></text></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header></section-header> | <b>Purposes</b><br>The five main purposes of these presentations are to<br>The five main purposes of these presentations are to<br>Provide a high-level overview of some of the foundations<br>of formal methods<br>The foundations<br>of formal methods may be applied<br>in various domains<br>Set the context for the remaining presentations at this<br>workshop<br>The foundations<br>The foundat |  |

East 24 ... Werner an worth

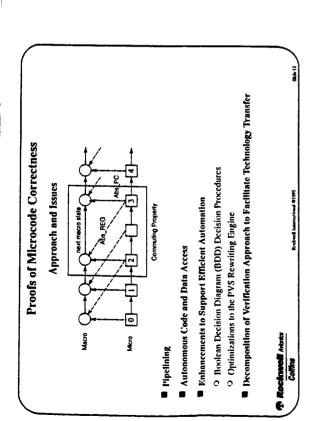

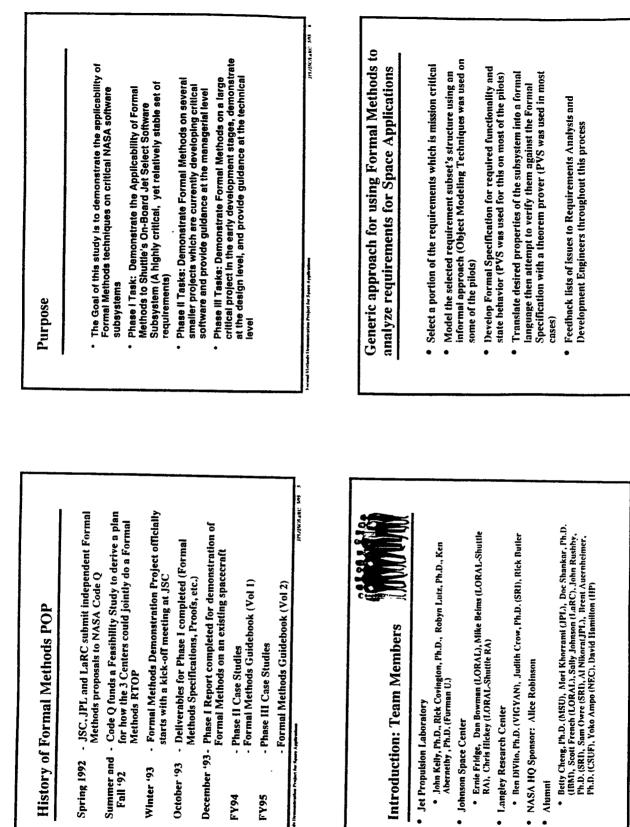

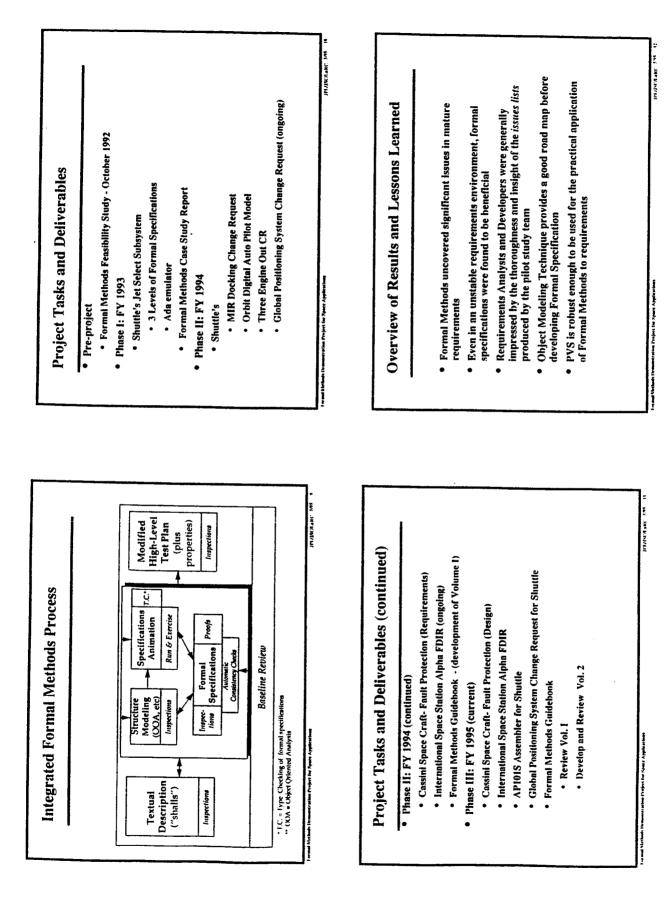

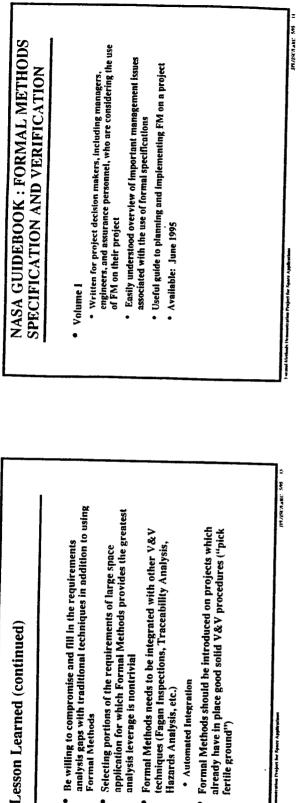

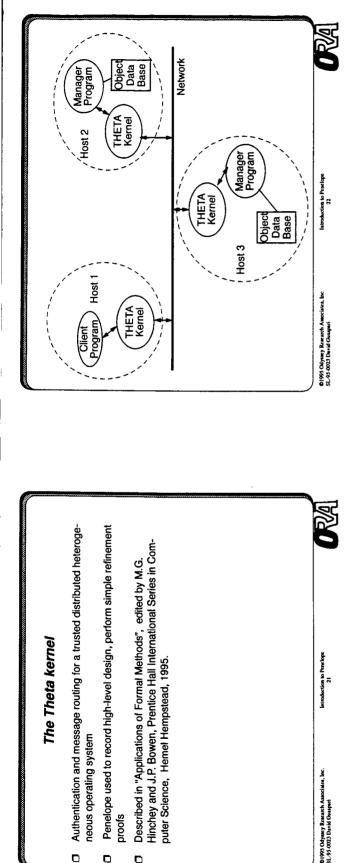

Comt