NASA Conference Publication 10052

### **NASA Formal** Methods Workshop 1990

(NASA-UP-10057) NASA FORMAL METHODS NORKSHUP, 1990 (NASA) 504 P LSCL 093 N91-17557 --THRU--N91-17570 Unclas 0319031

Compiled by Ricky W. Butler NASA Langley Research Center Hampton, Virginia

Proceedings of a workshop sponsored by the National Aeronautics and Space Administration, Washington, D.C., and held at Langley Research Center Hampton, Virginia August 20-23, 1990

63/01

November 1990

Langley Research Center Hampton, Virginia 23665-5225 •

.

### Contents

-

.

| Introduction                                                                                                     |

|------------------------------------------------------------------------------------------------------------------|

| Workshop Agenda                                                                                                  |

| List of Attendees                                                                                                |

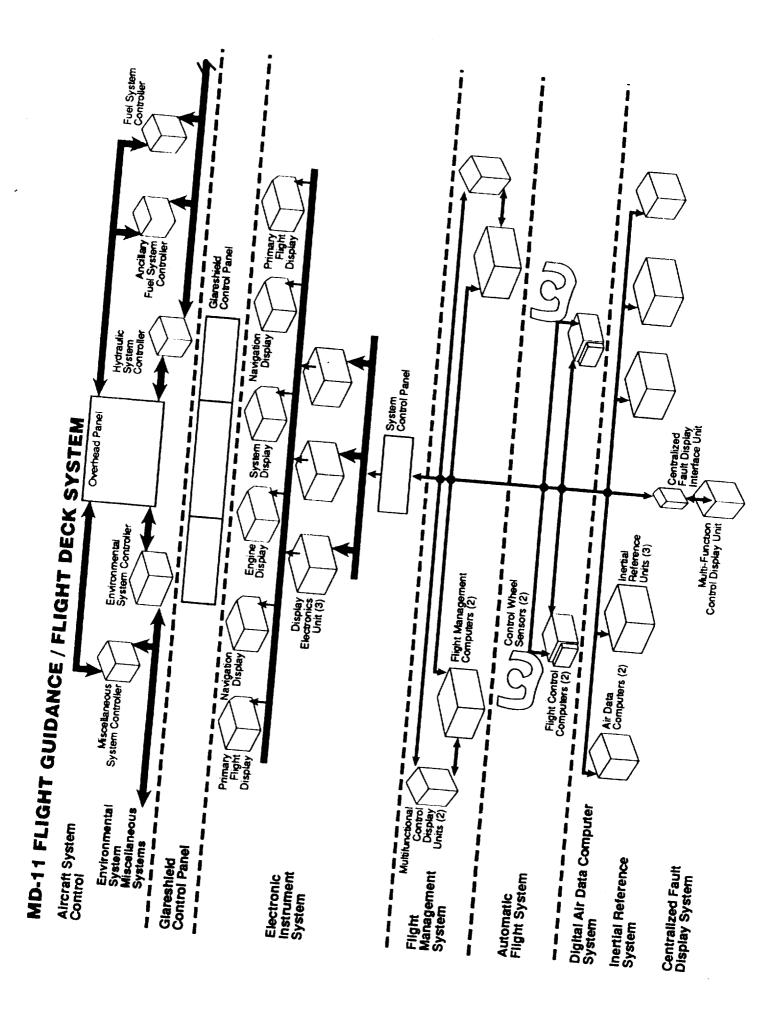

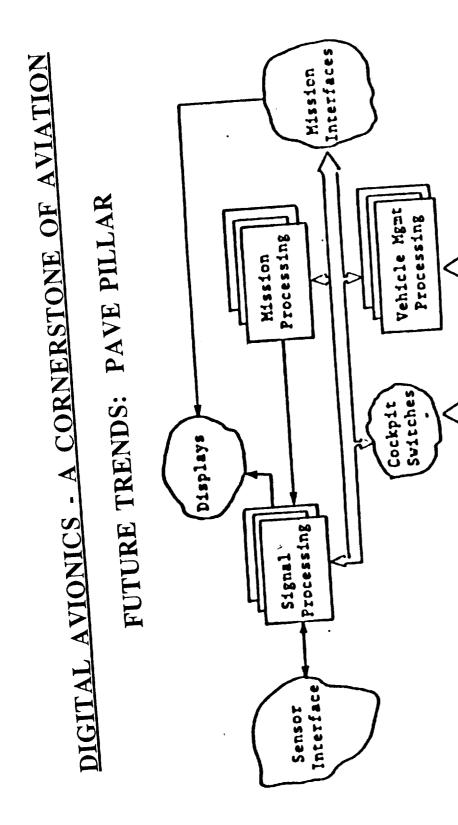

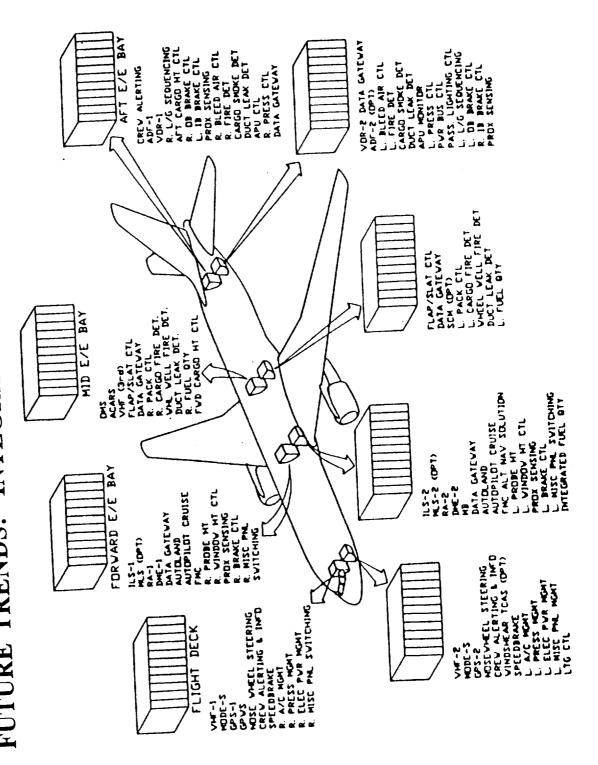

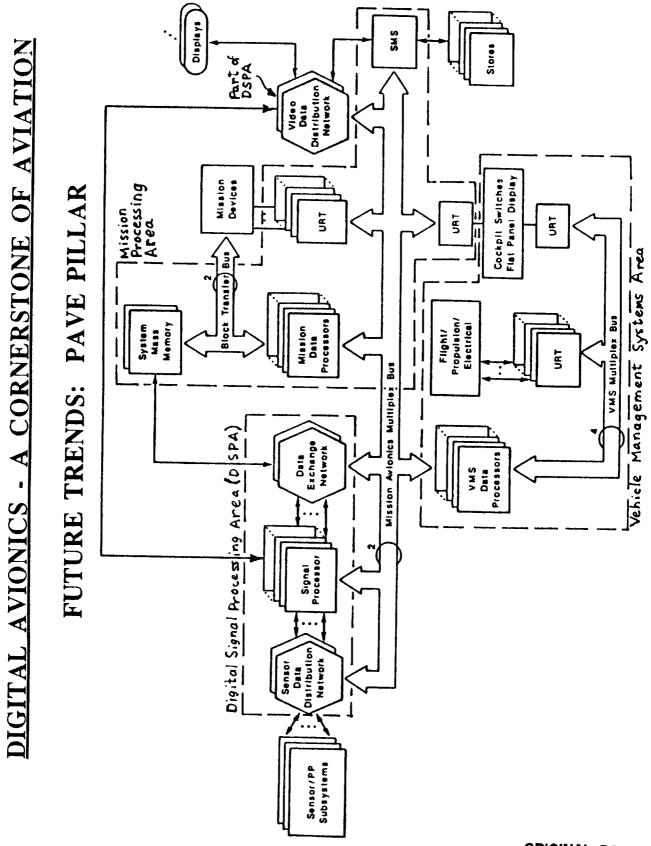

| Digital Avionics a Cornerstone of Avionics<br>by Chuck Meissner for Cary Spitzer (NASA)                          |

| Life Critical Digital Flight Control Systems<br>by James McWha (Boeing Military)                                 |

| Advanced Embedded Processing: Present and Future<br>by Jerry Cohen (Boeing Military)                             |

| MAFT: The Multicomputer Architecture for Fault Tolerance<br>by Roger Kieckhafer (U. Nebraska, Lincoln)           |

| Design For Validation<br>by Rick Butler (NASA)                                                                   |

| What FM can offer to DFCS design<br>by John Rushby (SRI International)                                           |

| What FM can offer to DFCS design<br>by Don Good (Computational Logic, Inc)                                       |

| High Level Design Proof of a Reliable Computing Platform<br>Ben DiVito (Vigyan)                                  |

| A Verified Model of Fault Tolerance<br>John Rushby (SRI International)                                           |

| The Design and Verification of a Fault-tolerant Circuit<br>Bill Bevier and Bill Young (Computational Logic, Inc) |

| Verifying an Interactive Consistency Circuit                                                                     |

| by Mandayam Srivas (Odyssey Research Associates) $\dots \dots \dots \dots \dots \dots \dots \dots \dots 295_{\leq d}$ | ×11                |

|-----------------------------------------------------------------------------------------------------------------------|--------------------|

| Hardware Verification at Computational Logic Inc.<br>by Warren Hunt (Computational Logic, Inc) 325                    | مديز               |

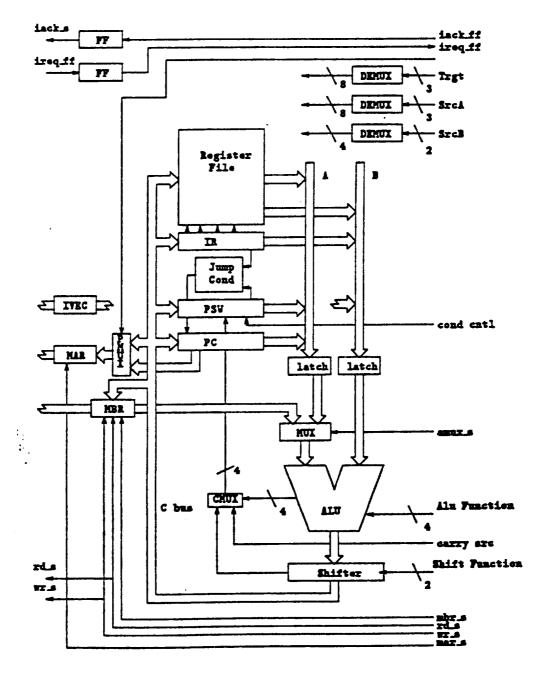

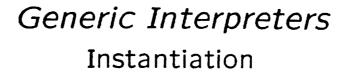

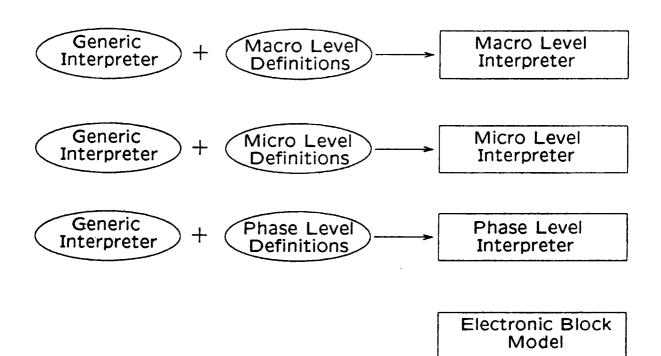

| Generic Interpreters and Microprocessor Verification<br>by Phil Windley (Univ. California, Davis)                     | × 2                |

| VIPER Project<br>by Clive Pygott and John Kershaw (Royal Signals and Radar Establishment) 380                         | 1514               |

| Mechanical Proofs of Fault-Tolerant Clock Synchronization<br>by N. Shankar and John Rushby (SRI International)        | 515                |

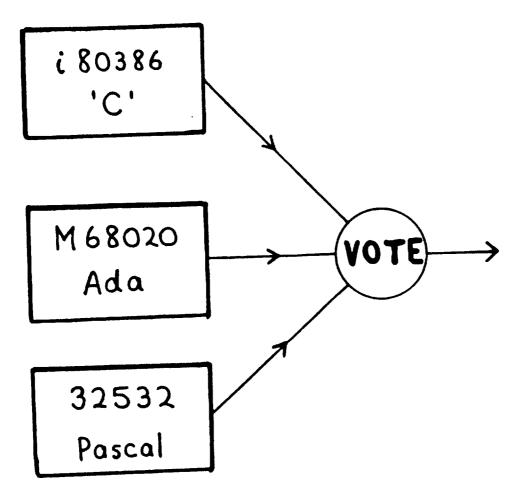

| An HOL Theory For Voting<br>by Paul Miner and Jim Caldwell (NASA) 442                                                 | 5/6                |

| Formally Specifying the Logic Of Automatic Guidance Control (Ada)<br>by David Guaspari (Odyssey Research Associates)  |                    |

| Verification of Floating-point Software<br>by Doug Hoover (Odyssey Research Associates)                               | 7 <sub>518</sub>   |

| C Formal Verification with Unix Communication and Concurrency<br>by Doug Hoover (Odyssey Research Associates)         | 95) <sub>[</sub> / |

\_\_\_\_

•

-

### Introduction

This publication contains copies of the material presented at the NASA Formal Methods Workshop held at Langley Research Center on August 20-23, 1990. The purpose of the workshop was to bring together the researchers involved in the NASA formal methods research effort for detailed technical interchange and to provide a chance for interaction with representatives from the U.S. government and the aerospace industry. The goals of the workshop were:

- Introduce the formal methods research teams to a broader view of the aerospace problem domain by industry presentations.

- Detailed technical exchange between formal methods research teams to define and characterize the verification problem for ultra-reliable life-critical flight control systems.

- Identification of aerospace problems which can benefit from formal methods and can serve as the basis of future research efforts.

The NASA effort in formal methods includes researchers at NASA LaRC, Computational Logic Inc., Odyssey Research Associates, SRI International, Boeing Military, Vigyan and the University of California at Davis and Irvine. Also NASA Langley is involved in a joint research effort with the UK Royal Signals and Radar Establishment as formalized in a Memorandum of Understanding between the two organizations.

Attendees at the workshop included NASA personnel, researchers from the four supporting contract organizations, RSRE personnel, invited speakers, and representatives from other government research organizations with interests in formal methods. Attendance was by invitation only.

### NASA Formal Methods Workshop Agenda (Aug 20-23, 1990)

### Day 1

| 8:00 - 8:20 am<br>8:20 - 8:30 am<br>8:30 - 8:45 am<br>8:45 - 9:30 am | Milt Holt<br>Ricky W. Butler<br>Chuck Meissner | Late Registration<br>Greeting by Chief of ISD<br>Workshop Objectives<br>Digital Avionics: A Cornerstone<br>of Aviation |

|----------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 9:30 - 10:15 am                                                      | James McWha                                    | Life Critical Digital<br>Flight Control Systems (DFCS)                                                                 |

| 10:15 - 10:30 am                                                     | BREAK                                          |                                                                                                                        |

| 10:30 - 11:30 am                                                     | Jerry Cohen                                    | Advanced Embedded Processing:<br>Present and Future                                                                    |

| 11:30 - 12:30 am                                                     | LUNCH                                          |                                                                                                                        |

| 12:30 - 1:30 pm                                                      | Roger                                          | MAFT: The Multicomputer Architecture                                                                                   |

| 1:30 - 2:00 pm                                                       | Kieckhafer<br>Rick Butler                      | for Fault Tolerance<br>Design For Validation                                                                           |

| 2:00 - 2:30 pm                                                       | BREAK                                          |                                                                                                                        |

|                                                                      | DILLAIN                                        |                                                                                                                        |

| 2:30 - 3:00 pm<br>3:00 - 3:30 pm<br>3:30 - 4:00 pm                   | Richard Platek<br>John Rushby<br>Don Good      | What FM can offer to DFCS design<br>What FM can offer to DFCS design<br>What FM can offer to DFCS design               |

Day 2

÷

-

.

---- OS verification ------

| 8:30 - 9:30 am<br>9:30 - 10:15 am | DiVito<br>Rushby | High Level Design Proof<br>of a Reliable Computing Platform<br>A Verified Model of Fault Tolerance |

|-----------------------------------|------------------|----------------------------------------------------------------------------------------------------|

| 10:15 - 10: <b>3</b> 0 am         | BREAK            |                                                                                                    |

|                                   |                  | Byzantine Generals                                                                                 |

| 10:30 - 11:30 pm                  | Bevier & Young   | The Design and Verification of<br>a Fault-tolerant Circuit                                         |

| 11:30 - 12:30 am                  | LUNCH            |                                                                                                    |

| 12:30 - 1:30 am                   | Srivas           | Verifying an Interactive<br>Consistency Circuit                                                    |

|                                   |                  | Microprocessor                                                                                     |

| 1:30 - 2:00 pm                    | Hunt             | Hardware Verification at<br>Computational Logic Inc.                                               |

| 2:00 - 2:30 pm                    | Windley          | Generic Interpreters and<br>Microprocessor Verification                                            |

| 2:30 - 3:00 pm                    | BREAK            |                                                                                                    |

| 3:00 - 4:00 pm<br>4:00 - 4:30 pm  |                  | w VIPER 2 & NODEN                                                                                  |

-----ks#c

.....

|                  |                              | Clock Synchronization                                                       |

|------------------|------------------------------|-----------------------------------------------------------------------------|

| 8:30 - 10:00 ai  | m Shankar/Rushby             | Mechanical Proofs of Fault                                                  |

| 10:00 - 10:30 a  | m Discussion                 | Tolerant Clock Synchronization                                              |

|                  |                              | Commercial Chips                                                            |

| 10:30 - 11:30 p  | m Levitt                     | Floating-pt. Coprocessor (Intel 8087)<br>DMA controller (Intel 8237A), etc. |

| 11:30 - 12:00 pr | n Caldwell/Carreno/<br>Miner | (rot in roceedings)                                                         |

|                  |                              | An HOL Theory For Voting                                                    |

| 12:00 - 1:00 pm  | LUNCH                        |                                                                             |

|                  |                              | — Code Verification ——-                                                     |

| 1:00 - 1:45 pm   | Guaspari                     | Formally Specifying the Logic Of                                            |

| 1:45 - 2:30 pm   | Hoover                       | Automatic Guidance Control (Ada)<br>Verification of Floating-point          |

| 2:30 - 3:00 pm   | Hoover                       | Software<br>C Formal Verification with Unix                                 |

|                  |                              | Communication and Concurrency                                               |

| 3:00 - 3:30 pm   | BREAK                        | · ·                                                                         |

| 3:30 - 5:00 pm   | Planning                     |                                                                             |

### Day 4

8:30 - 12:00 pm Discussion

### NASA FM Workshop Attendees

-

| Deepak Kapur<br>Dale Johnson<br>Andy Moore<br>Karl Levitt<br>Sally Johnson<br>Richard Platek<br>Bill Young<br>Don Good<br>Warren Hunt<br>Jim Caldwell<br>Mark Bickford<br>Mark Saaltink<br>Bill Legato<br>Kang Shin<br>Chuck Meissner<br>Pete Saraceni<br>Roger Kieckhafer<br>Doug Hoover<br>David Guaspari<br>Tom Schubert<br>Mark Ardis<br>Clive Pygott<br>John Kershaw<br>David Musser<br>Phil Windley<br>John Knight<br>Rick Kuhn<br>Dave Eckhardt<br>John McHugh<br>Milt Holt<br>Ben DiVito | ORA<br>ORA<br>UC Davis<br>SEI<br>RSRE, Malvern<br>RSRE, Malvern<br>RPI<br>U. Idaho<br>U. Va.<br>NIST<br>NASA, LaRC<br>CLI<br>NASA, LaRC<br>Vigyan/NASA | (512)322-9951         bevier@cli.com           (518)442-4281         kapur@albanycs.albany.edu           (617)271-8894         (202)767-6698           (202)767-6698         moore@itd.nrl.navy.mil           (916)752-0832         levitt@ucdavis.edu           (804)864-6204         scj@air16.larc.nasa.gov           (607)277-2020         richard%oravax.uucp@cu-arpa.cs.cornell.edu           (512)322-9951         young@cli.com           (512)322-9951         hunt@cli.com           (804)864-6214         jlc@air16.larc.nasa.gov,caldwell@cs.cornell.edu           (607)277-2020         ??? %oravax.uucp@cu-arpa.cs.cornell.edu           (613)238-7900         mark@ora.on.ca           (301)688-4229         (313)763-0391           (313)763-0391         kgshin@eecs.umich.edu           (607)277-2020         rogerk@fergvax.unl.edu           (607)277-2020         rogerk@fergvax.uucp@cu-arpa.cs.cornell.edu           (607)277-2020         rogerk@fergvax.uucp@cu-arpa.cs.cornell.edu           (607)277-2020         rogerk@fergvax.uucp@cu-arpa.cs.cornell.edu           (607)277-2020         rogerk@fergvax.uucp@cu-arpa.cs.cornell.edu           (607)277-2020         rogerk@fergvax.uucp@cu-arpa.cs.cornell.edu           (607)277-2020         rogerk@fergvax.uucp@cu-arpa.cs.cornell.edu           (607) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| John McHugh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CLI                                                                                                                                                    | (804)864-1596                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Milt Holt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NASA, LaRC                                                                                                                                             | (804)864-4883 bld@air16.larc.nasa.gov                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

5,-06 P-24 4.30 × 1 Ó

### **DIGITAL AVIONICS**

## A CORNERSTONE OF AVIATION

by Cary R. Spitzer NASA Langley Research Center Presented to the NASA Formal Methods Workshop by

Charles W. Meissner, Jr.

# DIGITAL AVIONICS - A CORNERSTONE OF AVIATION

INTRODUCTION: Avionics Roles

Communication

. HF and VHF

Satellite

. Data Links

Navigation

.

Ground-based systems

.

- systems Inertial and satellite-based .

- Goal: <u>Autonomous operation!!!</u>

L

# DIGITAL AVIONICS - A CORNERSTONE OF AVIATION

INTRODUCTION

**CURRENT EXAMPLES**

**CURRENT ISSUES**

FUTURE TRENDS

INTERNATIONAL SCENE

SUMMARY

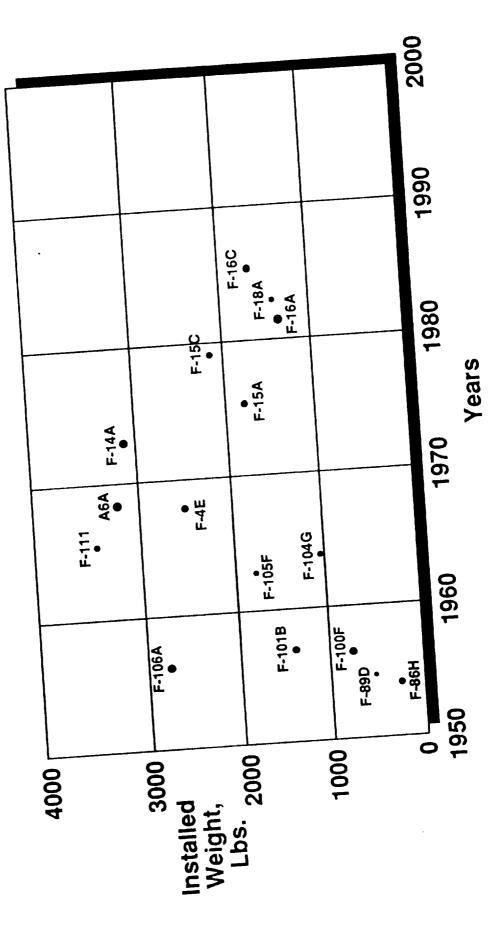

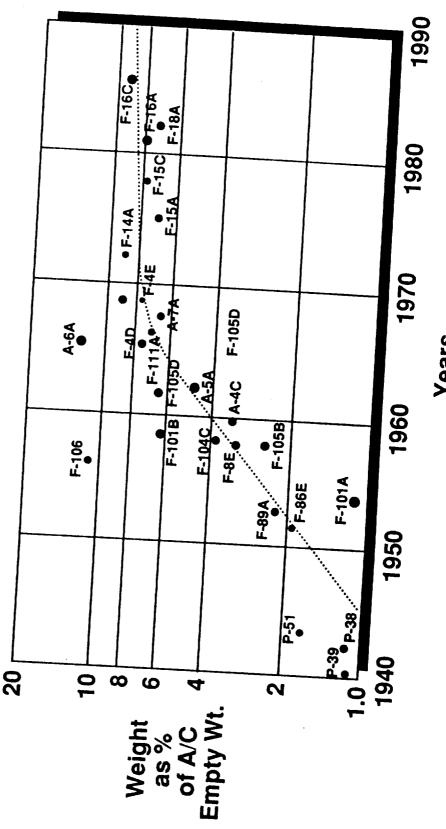

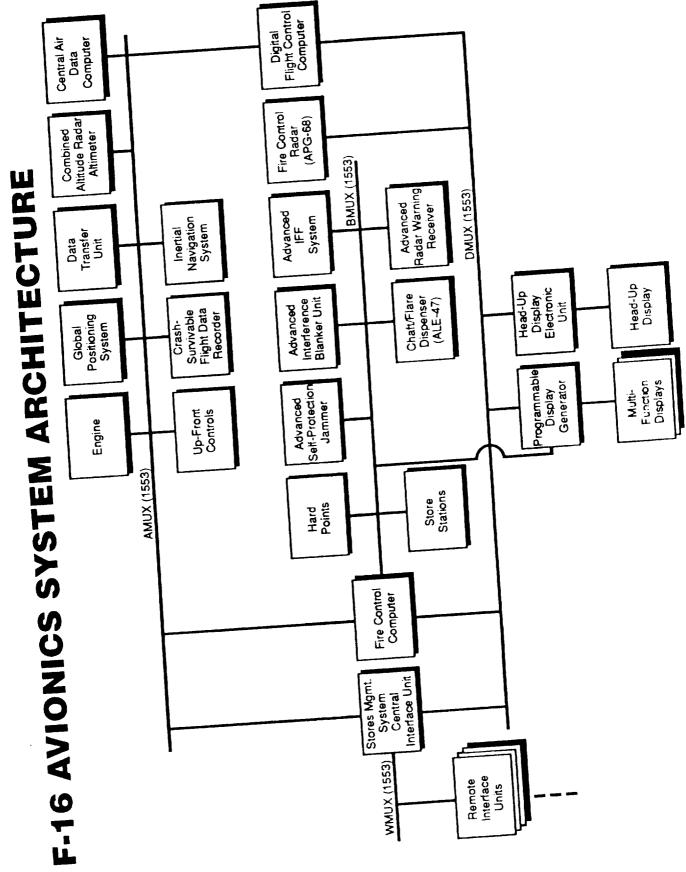

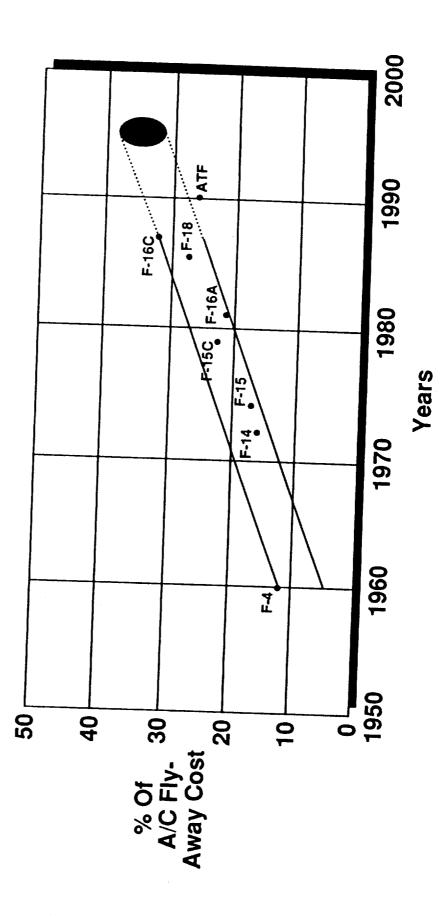

### FIGHTER INSTALLED AVIONICS WEIGHT

| DIGITAL AVIONICS - A CORNERSTONE OF AVIATION<br>INTRODUCTION: Avionics Roles<br>- Fly-by-wire flight controls<br>- Historically used for stability & control augmentation<br>- Not flight critical | <ul> <li>Emerging as a flight critical system</li> <li>Driven by performance and economic demands</li> <li>F-16, A-320, B-777</li> </ul> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

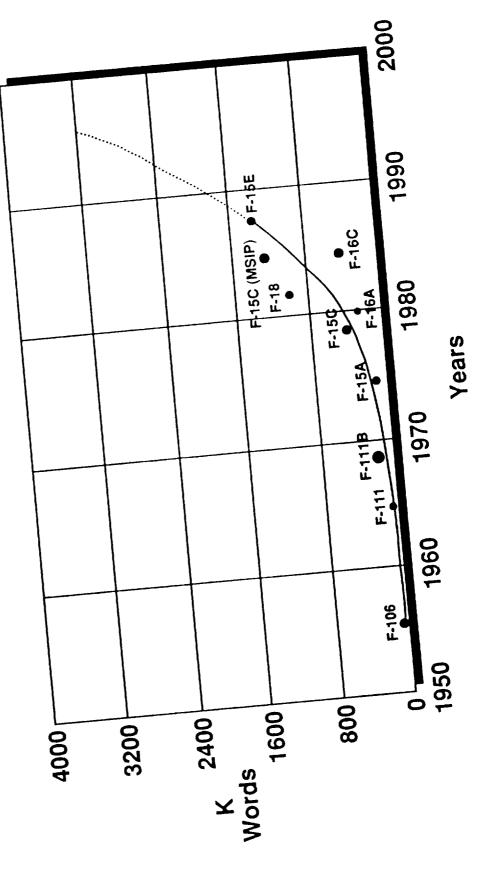

## TOTAL ON BOARD COMPUTER CAPACITY (OFP)

## TRENDS IN AVIONICS ABOARD FIGHTER/ATTACK AIRCRAFT

Years

-----

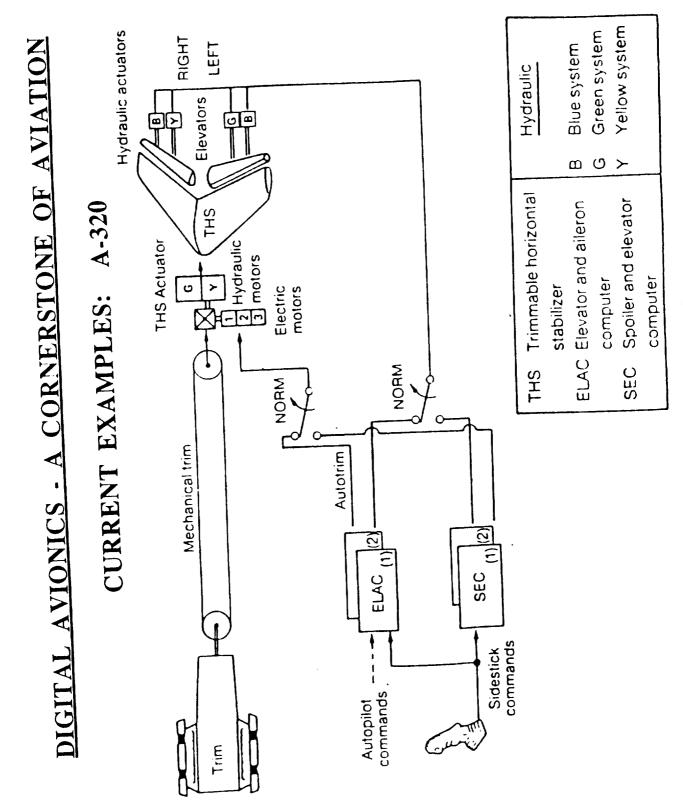

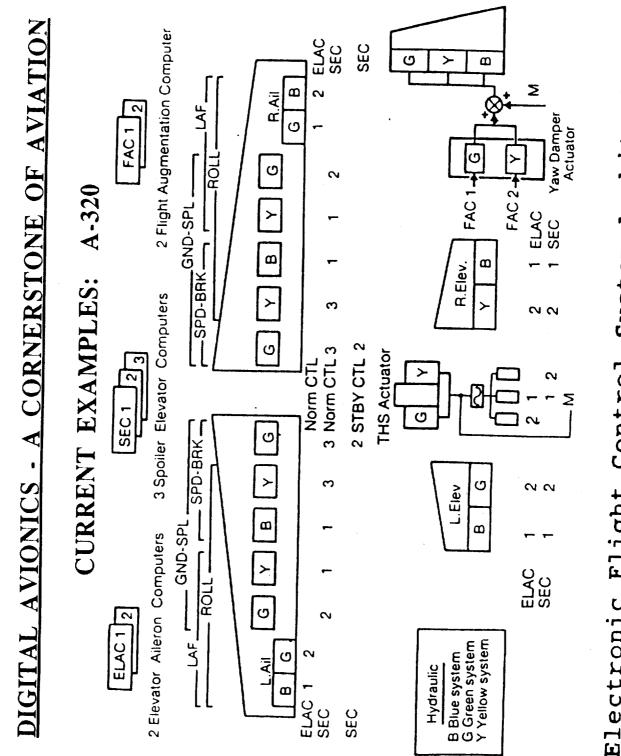

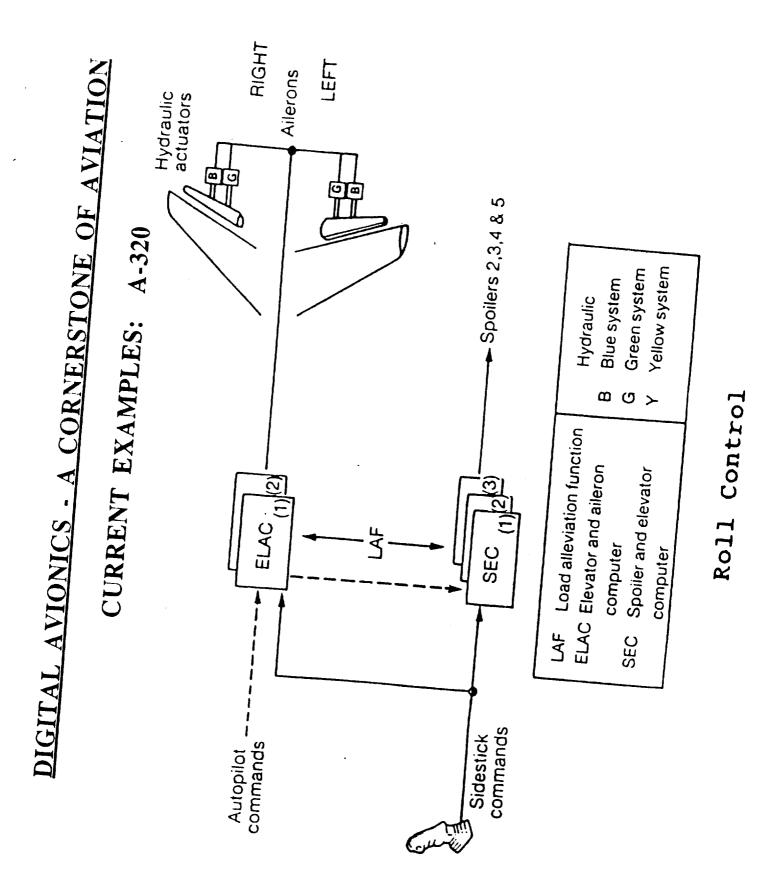

Pitch Control

System Architecture Control Electronic Flight

DIGITAL AVIONICS - A CORNERSTONE OF AVIATION Rudder Hydraulic / æ υ 7 Yellow system Green system Artificial Blue system feel Mech.stop CURRENT EXAMPLES: A-320 Hydraulic × لالح U Σ Σ mΩ≻ Travel limitation Flight augmentation computer Rudder trim Yaw damper Motor actuator FACS FAC Rudder trim Σ yaw commands Autopilot ELAC Rudder pedals J

Yaw Control

### DIGITAL AVIONICS - A CORNERSTONE OF AVIATION CURRENT ISSUES: Hardware

. Proof of fault tolerance, high reliability Modeling of complex systems

.

Growing concern due to composite aircraft, interference Electromagnetic

.

increased emission of RF, and smaller electronic element sizes

Vehicle Mgmt Interfaces/<

| TION                                                                     | ivil                                                                                                                | & design                                                                                                                              |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| DIGITAL AVIONICS - A CORNERSTONE OF AVIATION<br>CURRENT ISSUES: Software | <ul> <li>Developing competency in Ada</li> <li>Mandated for DoD, Space Station Freedom, civil transports</li> </ul> | Computer-Aided Software Engineering (CASE) Tools - Capabilities for real-time software analysis { - Tool validation - Tool validation |

.

٢

.

.

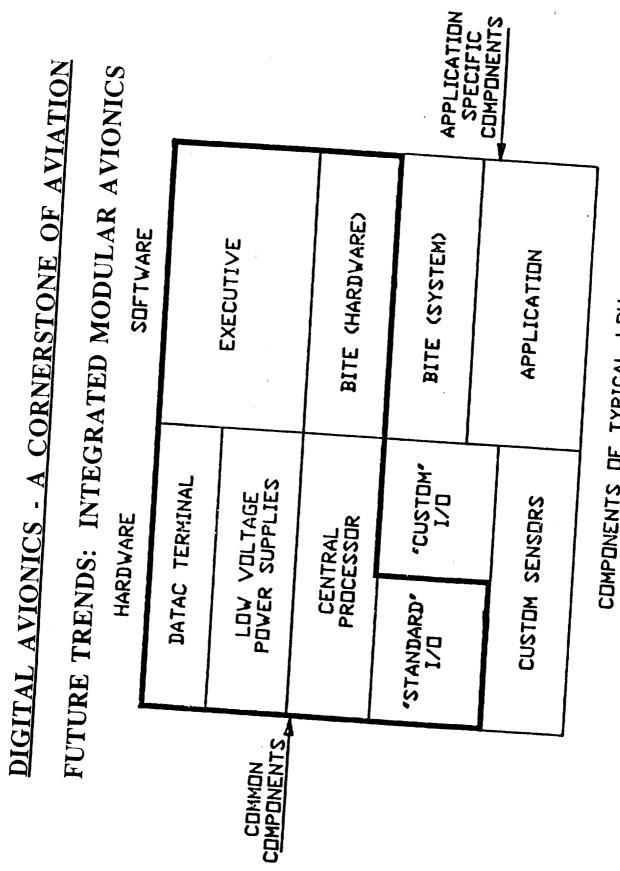

DIGITAL AVIONICS - A CORNERSTONE OF AVIATION FUTURE TRENDS: INTEGRATED MODULAR AVIONICS

URIGINAL PAGE IS OF POOR QUALITY

ORIGINAL PAGE IS OF POOR QUALITY DIGITAL AVIONICS - A CORNERSTONE OF AVIATION FUTURE TRENDS: Supporting Technologies

Flat panel, full color, liquid crystal displays

- Replacing CRTs

- Advanced formats; not electronic steam gauges ŧ

Higher speed data buses

programs pioneer Artificial intelligence

- Faultfinder

- Diverter 1

- Pilot's Associate 8

COMPONENTS OF TYPICAL LRU

DIGITAL AVIONICS - A CORNERSTONE OF AVIATION

INTERNATIONAL SCENE: Japan

- An emerging competitor in the world market

- displays, Historically has been component oriented: t

microprocessors, etc.

- Lack system design and analysis, & software capabilities 1

- FS-X program will help to build a foundation for

military & civil avionics

an avionics has established a committee to define MITI

technology development plan

| DIGITAL AVIONICS - A CORNERSTONE OF AVIATION | Leading firms are GEC Avionics, Smiths Industries, Sextant, & | Extremely capable; serious competition for U.S. firms | GEC Avionics will build the B-777 flight control system | European Community 92 will strengthen competitive threat |

|----------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------|

| INTERNATIONAL SCENE: Europe                  | Aerospatiale                                                  | - Build most of the Airbus avionics                   | - Build flight controls for Jaguar and YC-14            |                                                          |

\_\_\_\_

----

# DIGITAL AVIONICS - A CORNERSTONE OF AVIATION

### SUMMARY

- Continually expanding role for avionics 1

- . Flight critical avionics are here

- Strong emphasis on Ada

- architectures emerging Module-based I

- developed being Artificial intelligence applications

- Significant competitive threat to U.S. firms from ł

Europe & Japan

52 -08 P-9.4 580815

# LIFE-CRITICAL DIGITAL FLIGHT CONTROL SYSTEMS

### **JIM McWHA**

CHIEF ENGINEER - FLIGHT CONTROLS BOEING COMMERCIAL AIRPLANE GROUP N91-17561

AUGUST 20, 1990

# LIFE-CRITICAL DIGITAL FLIGHT CONTROL SYSTEMS

### INDUSTRY STATUS

DIGITAL AUTOPILOT SYSTEMS WERE FIRST CERTIFICATED FOR USE ON COMMERCIAL

AIRPLANES IN THE LATE 1970'S

THE A-320 AIRPLANE WAS THE FIRST COMMERCIAL AIR TRANSPORT AIRPLANE TO BE CERTIFICATED WITH A FLY BY WIRE PRIMARY FLIGHT CONTROL SYSTEM

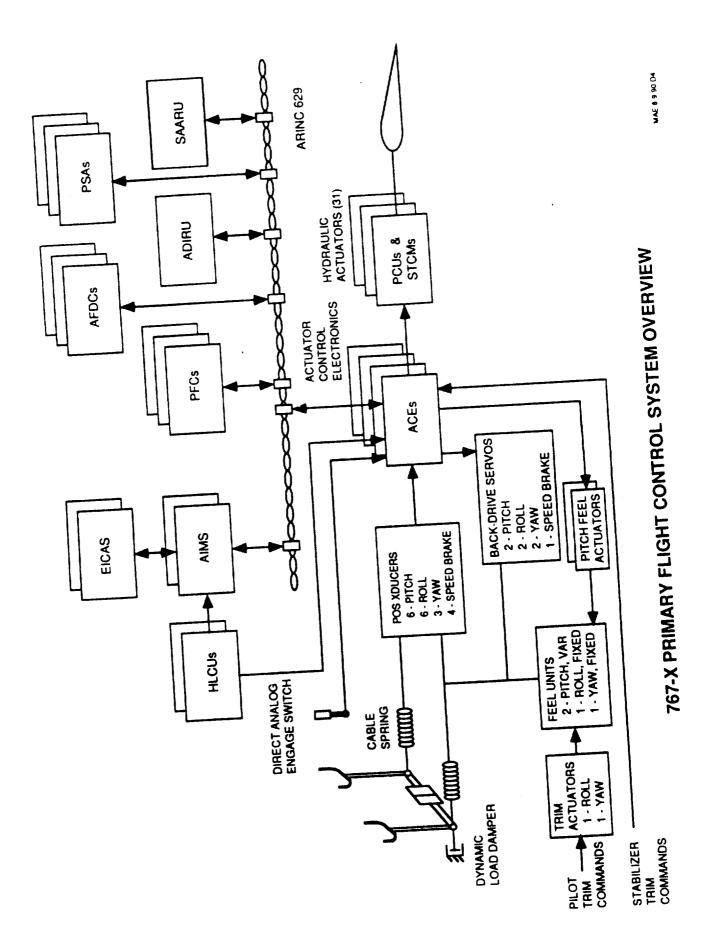

BOEING WILL HAVE ALL FLY BY WIRE FLIGHT CONTROLS ON THE 767-X (777) AIRPLANE

# LIFE-CRITICAL DIGITAL FLIGHT CONTROL SYSTEMS

- o DEFINITION

- o SAFETY

- O INDUSTRY STATUS

- **o PROGRAM PHASES**

۳

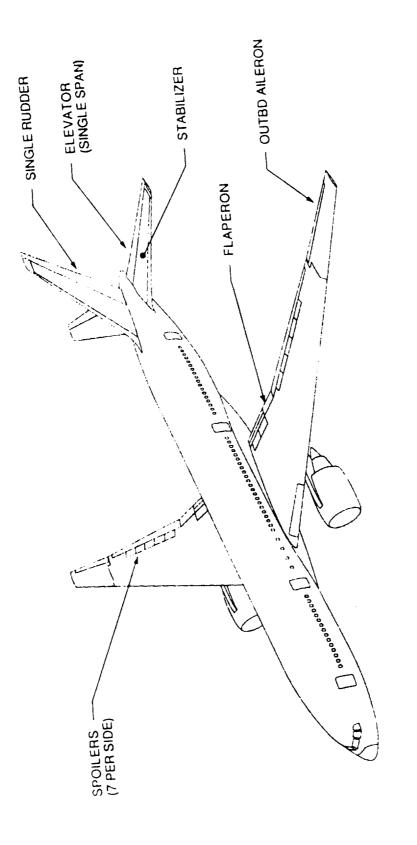

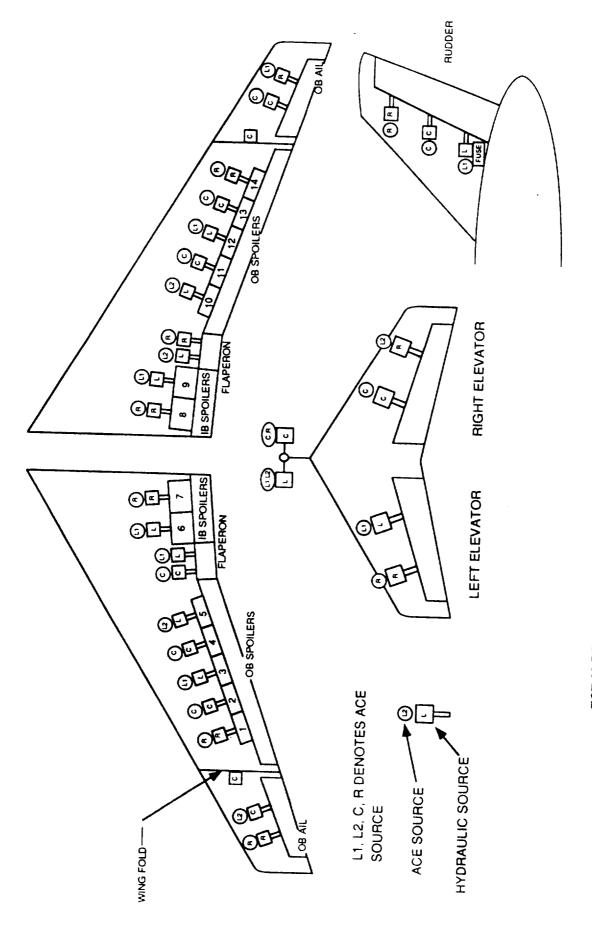

767-X PRIMARY FLIGHT CONTROL SURFACES

ţ

#### DEFINITION

A CONTROL SYSTEM IMPLEMENTED IN DIGITAL COMPUTER TECHNOLOGY WHICH Has a function which if not performed as intended is life threatening

AN AUTOPILOT USED FOR AUTOMATIC LANDING IN LOW VISIBILITY CONDITIONS EXAMPLES:

AN AIRPLANE CONTROL SYSTEM IMPLEMENTED WITHOUT **CONTROL CABLES:**

FLY BY WIRE

FLY BY LIGHT

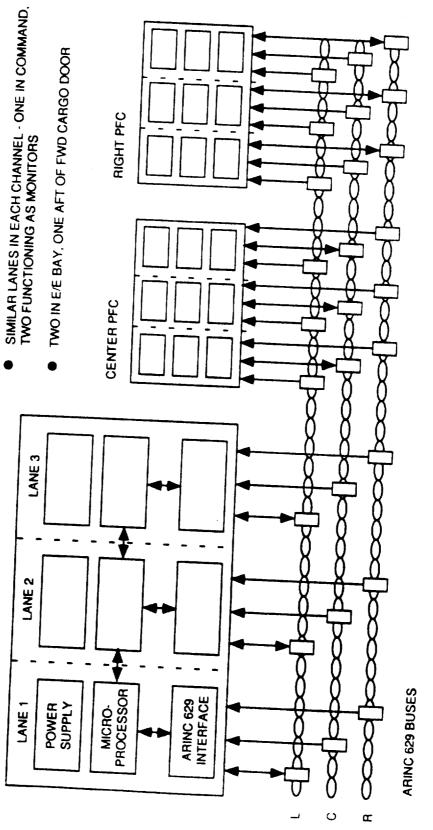

LEFT PFC

.

DISSIMILAR CHANNELS - LEFT, CENTER, RIGHT

PRIMARY FLIGHT COMPUTER ARCHITECTURE

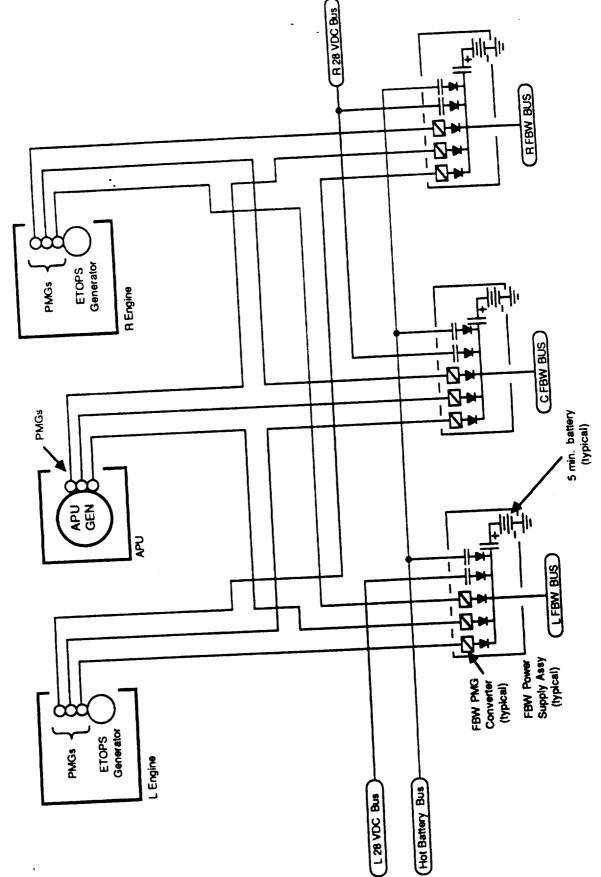

767-X ELECTRICAL POWER SYSTEM FLIGHT CRITICAL DC

767-X PRIMARY FLIGHT CONTROLS HYDRAULIC / ACE DISTRIBUTION

#### SAFETY

FEDERAL AVIATION ADMINISTRATION (FAA) REGULATIONS DEFINE THE BASIC SAFETY

**CRITERIA:**

NO SINGLE FAILURE OR COMBINATION OF FAILURES WHICH ARE NOT CONTINUED SAFE FLIGHT AND LANDING OF THE AIRPLANE SHOWN TO BE EXTREMELY IMPROBABLE SHALL PREVENT FAR 25.1309

EXTREMELY IMPROBABLE - PROBABILITY OF 1 × 10<sup>-9</sup> OR LESS PER FLIGHT HOUR OR

EVENT

#### SAFETY

FEDERAL AVIATION ADMINISTRATION (FAA) REGULATIONS DEFINE THE BASIC SAFETY **CRITERIA:**

NO SINGLE FAILURE OR COMBINATION OF FAILURES WHICH ARE NOT CONTINUED SAFE FLIGHT AND LANDING OF THE AIRPLANE SHOWN TO BE EXTREMELY IMPROBABLE SHALL PREVENT FAR 25.1309

EXTREMELY IMPROBABLE - PROBABILITY OF 1 × 10<sup>-9</sup> or less per flight hour or

EVENT

\_\_\_\_\_

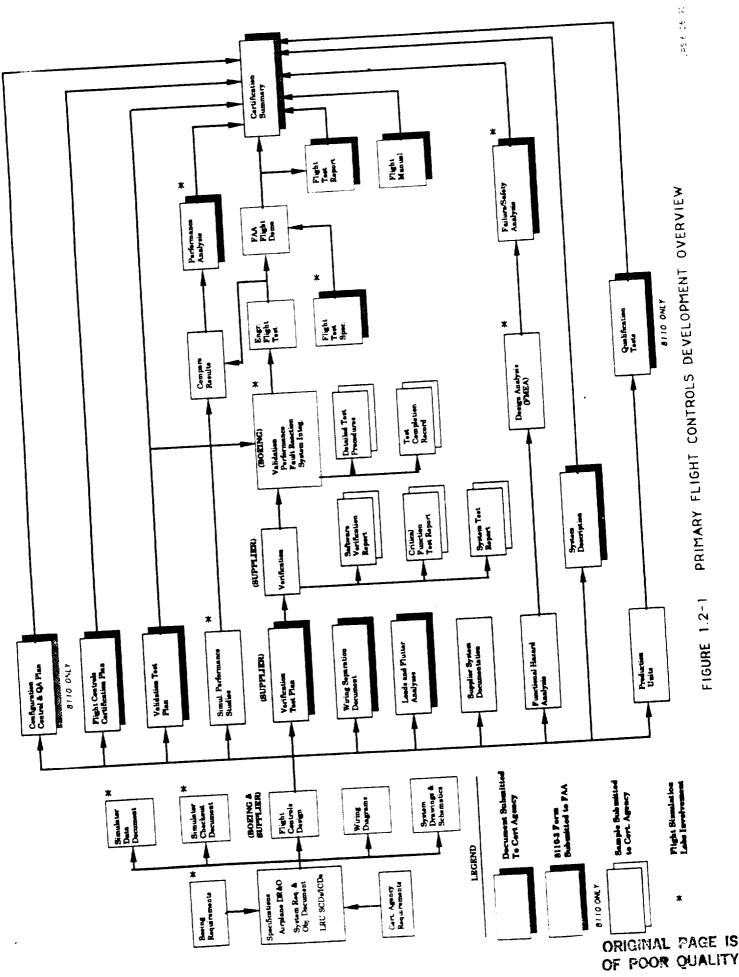

## **PROGRAM PHASES - REQUIREMENTS DEFINITION**

TOP DOWN STRUCTURED PROCESS:

AIRPLANE LEVEL REQUIREMENTS TOP LEVEL DESIGN REQUIREMENTS AND OBJECTIVES

| CERTIFICATION REQUIREMENTS<br>FUNCTIONAL REQUIREMENTS<br>INTEGRITY REQUIREMENTS<br>ARCHITECTURAL CONSIDERATIONS | EXPANSION OF SYSTEM REQUIREMENTS TO A<br>LEVEL WHICH CAN BE IMPLEMENTED IN A TARGET<br>DIGITAL COMPUTER OR COMPUTERS |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| SYSTEM REQUIREMENTS                                                                                             | SOFTWARE REQUIREMENTS                                                                                                |

## PROGRAM PHASES - REQUIREMENTS DEFINITION (CONT)

SPECIFIC HARDWARE/SOFTWARE TO IMPLEMENT THE REQUIREMENTS WHICH EVOLVE OUT OF THE USE OF SOFTWARE REQUIREMENTS **DETAILED DESIGN** REQUIREMENTS

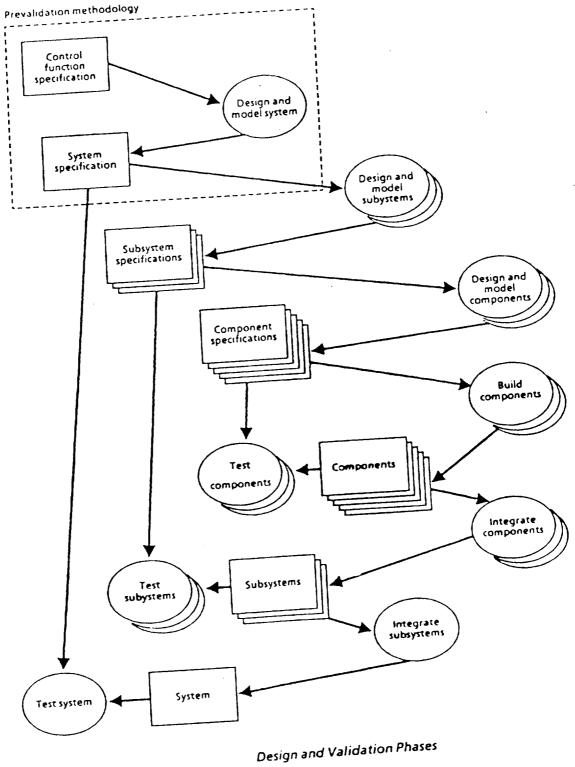

### **PROGRAM PHASES - DESIGN AND DEVELOPMENT**

| vo requirements<br>processing speed<br>memory size<br>etc | INDUSTRY/COMPANY STANDARD<br>SUPPORT SOFTWARE AVAILABILITY AND MATURITY<br>LONG TERM MAINTENANCE<br>ETC | TYPICALLY AN INCREMENTAL BUILD PROCESS<br>HARDWARE - QUALIFICATION TESTING - RTCA DO-160<br>INCREMENTAL SOFTWARE LOADS - VENDOR AND AIRFRAME<br>SYSTEMS INTEGRATION / IRON BIRD<br>AIRPLANE - GROUND AND FLIGHT |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HARDWARE SELECTION                                        | PROGRAMMING LANGUAGE                                                                                    | CODE GENERATION<br>TESTING                                                                                                                                                                                      |

### **PROGRAM PHASES - VERIFICATION**

GUIDELINE DOCUMENT

**RTCA DOCUMENT DO-178A**

VERIFICATION PROCESSES ARE A FUNCTION OF SYSTEM CRITICALITY

**CRITICAL SYSTEM**

REQUIREMENTS HAVE BEEN IMPLEMENTED COMPLETELY A FORMAL PROCESS OF ASSURING THAT ALL SOFTWARE

AND EXCLUSIVELY

### **PROGRAM PHASES - VALIDATION**

A PROCESS OF ASSURING THAT ALL SYSTEM REQUIREMENTS HAVE BEEN IMPLEMENTED CORRECTLY

O ANALYSES

| HAZARD ASSESSMENT AND FAILURE<br>ANALYSIS TO ASSURE THAT REQUIREMENTS<br>OF FAR 25.1309 ARE SATISFIED | ASSURANCE THAT SYSTEM PERFORMS<br>INTENDED FUNCTION WITHIN ACCEPTABLE<br>LIMITS UNDER ALL ALLOWABLE<br>ENVIRONMENTAL AND TOLERANCE<br>CONDITIONS |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| SAFETY ANALYSIS                                                                                       | PERFORMANCE<br>ANALYSIS                                                                                                                          |

| LIFE-CRITICAL DIGITAL FLIGHT CONTROL SYSTEMS | ON (CONT)                          | TEST TO ISOLATE ERRORS AND PROBLEMS<br>BEFORE FLIGHT TEST. TEST UNDER NORMAL AND<br>FAILURE CONDITIONS | TEST WITH AS MANY INTERFACING SYSTEMS AS<br>POSSIBLE TO ENSURE COMPATIBILITY | CHECK OF SYSTEMS INSTALLED IN AN AIRPLANE<br>INCLUDING EMI/HIRF TESTS | COMPREHENSIVE TEST OF PERFORMANCE IN<br>FLIGHT UNDER A VARIETY OF CONDITIONS USED<br>TO CROSS CHECK SIMULATION RESULTS -<br>AUTOLAND SYSTEM COULD REQUIRE 200-300<br>LANDINGS OVER AN 8 MONTH PERIOD |

|----------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIFE-CRITICAL DIG                            | PROGRAM PHASES - VALIDATION (CONT) | LABORATORY TESTING                                                                                     | SYSTEMS INTEGRATION<br>TESTING                                               | AIRPLANE GROUND<br>TESTING                                            | AIRPLANE FLIGHT<br>TESTING                                                                                                                                                                           |

|                                              | PROG                               | 0                                                                                                      | 0                                                                            | 0                                                                     | 0                                                                                                                                                                                                    |

### **PROGRAM PHASES - CERTIFICATION**

THE PROCESS OF DEMONSTRATING TO THE REGULATORY AUTHORITIES THAT ALL SAFETY AND PERFORMANCE REQUIREMENTS ARE SATISFIED

STARTS WITH A CERTIFICATION PLAN WHICH:

IDENTIFIES REGULATIONS AND ACCEPTABLE MEANS OF COMPLIANCE METHODS

DESCRIBES PROPOSED METHODS OF ESTABLISHING COMPLIANCE

DESCRIBES THE METHODS AND PROCESSES TO BE USED TO ASSURE AN ORDERLY AND CONTROLLED DESIGN AND DEVELOPMENT PROCESS

FOLLOW ON SPECIALIST MEETINGS

PERFORMANCE AND INTEGRITY DEMONSTRATIONS

### **PROGRAM PHASES - CERTIFICATION (CONT)**

**CERTIFICATION SUMMARY**

CONFIRMS COMPLETE IMPLEMENTATION OF THE PROCESSES IDENTIFIED IN THE **CERTIFICATION PLAN**

PROVIDES A MEANS FOR ESTABLISHING VERIFICATION AND VALIDATION COVERAGE

| ſ           |           |                           |                                    |                               |                                 |

|-------------|-----------|---------------------------|------------------------------------|-------------------------------|---------------------------------|

|             | 1995      | Type Cert.                | Final Cert.<br>Data                |                               | 767-X<br>FLIGHT<br>TEST         |

|             | 1994      | Rollout                   | Fail/Safety,<br>System Des.        |                               | Iron<br>Bird<br>Test            |

|             | 1993      | FAA Interim<br>Type Board | Fa<br>Syst                         | 757 Flight<br>Test            | gn<br>Build<br>767-X<br>Units   |

| -<br>-<br>- | 1992      | FAA Interim<br>Type Board | FAA Cert Plan<br>Approval<br>11/29 | Iron Bird<br>Test             | Production Design<br>Validation |

| -           | 1990 1991 | Type Cert. Appl.          | Plan<br>4/1                        | PRE-PRODUCTION<br>DEVELOPMENT |                                 |

|             | 19        | т <sub>ур</sub>           | Certification<br>Documentation     | 757 PFCS                      | 767-X<br>PFCS                   |

### 767-X PFCS Schedule

,

BRD8/10/90

#### K

52 53-05 RHD 319684

. 17 7

## Advanced Embedded Processing Present and Future

The Boeing Company G.C. Cohen

N91-17562

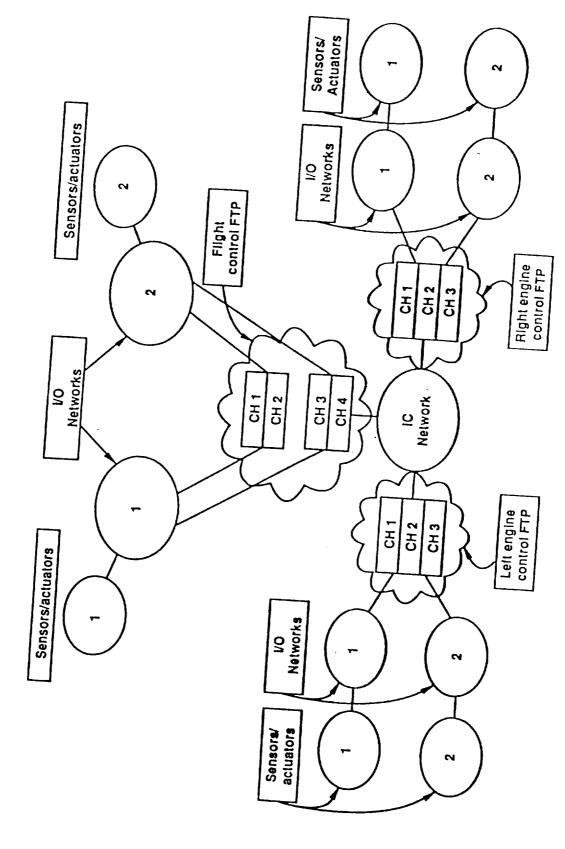

# Integrated Airframe/Propulsion Control System Architecture (IAPSA II)

Began: July 26, 1985 Ended: April 1, 1990

### Goals of the Program

- Design and validation methodology for systems architecture

- 2. Critical validation issues simulated in Airlab 3. System design

- System specification 4.

- Small-scale system testing <u></u>.

ł

.

#### Methodology

----

C0006-01.01 L7130 D34 Slide 6

### Why a Methodology

C0006-01.02 L7130 D35 ai

#### Problem

Interrelationships difficult to specify in terms of meaningful requirements

- Normal mode

- Failure mode

- Unless contractor/vendor team takes a systems approach, system will be overdesigned and still may not meet the requirements

### Methodology Elements

- Requirements

- Specifications

- Design

- Automation

- Guidelines

- Building blocks

- Reliability

- Performance

- Design for validation

- Design for cost

- Proof of correctness

- Testing

- Traceability

- Availability

- Survivability

- Maintainability

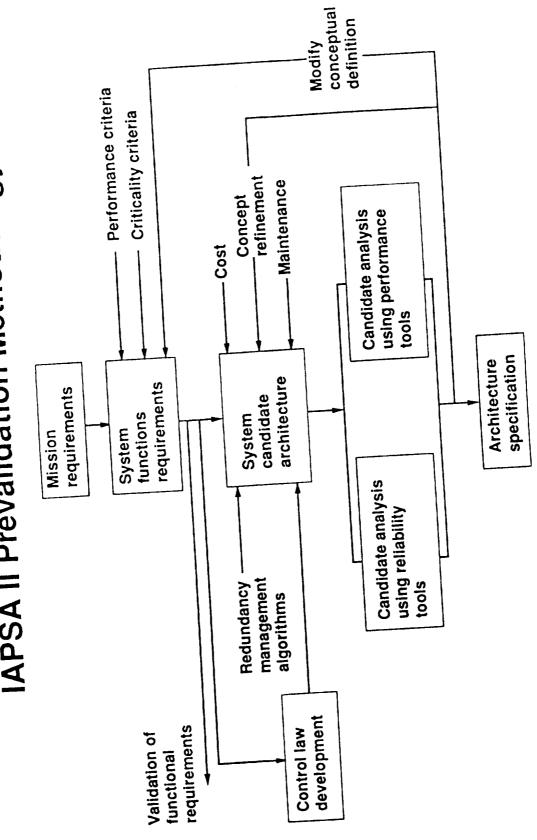

**IAPSA II Prevalidation Methodology**

Boeing Military Airplanes

C0006-10.04 L7130 D35 md2

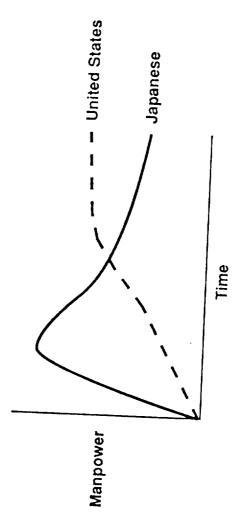

### **Prevalidation Methodology**

- Early evaluation exposes system weaknesses

- Reliability and performance analysis versus staffing level unresolved

- Methodology allows assessment of cost and technical risk

- Seems to mirror Japanese staffing concept

C0006-01.03 L7130 D35 pp

00041-1558

### Building-Block Considerations Contractor/Subcontractor Relationships

- Requires different approach to subcontractors •

- Need to develop:

- Functional specification

- · Reliability attributes

- Performance attributes

- · Requirements only will not suffice

- Subtleties of building-block interrelationships important

C0006-01.01 L7130 D34 Silde 8

#### Building-Block Considerations Contractor/Subcontractor Relationships (continued)

- Enforcement of rigor on the vendors

- Do we need a two-step procedure with vendors—

- During building-block definition

- During hardware/software bid on system

#### Methodology

Incomplete

- Additional tools

- Maintainability

- Availability

- Survivability

- Cost

- Software

- Tie in to top-level system design

- Relationship between full nonlinear simulation and performance model •

- Hardware and software build—subsystem validation and verification

- Lab testing

- Flight testing

C00006-01.01 L7130 D34 Slide 10

#### Tools

Model development—candidate architecture definition Major effort on

- - How system works

- Brief, concise, easy to generate

- Must include redundancy management operation

- Output data interpretation

- Complex

- Very time consuming

### Performance Modeling

- Difficult to simulate

- Conceptual problem

- Difficult to implement

- Detail of simulation is based upon judgement

- Simulation can validate system architecture

- Verification of model with architecture description

- Simulation used through life cycle

- Unexpected insight via performance simulation

C0006-01.01 L7130 D34 Slide 1

### **Reliability Modeling**

Methodology goal: rapid evaluation of architecture alternatives

- Current evaluation cycle too slow

- Tools available for ultrareliable systems

- Short-duration safety

- Long-duration reliability also important

- **Operation with failures**

- Common evaluation tool and similar models (safety, mission, etc.) desirable (mandatory?)

- Level of detail and model simplification currently an art

- Strong pressure toward small and simple models

- ASSIST/SURE supports techniques for short-duration problems (long-duration?)

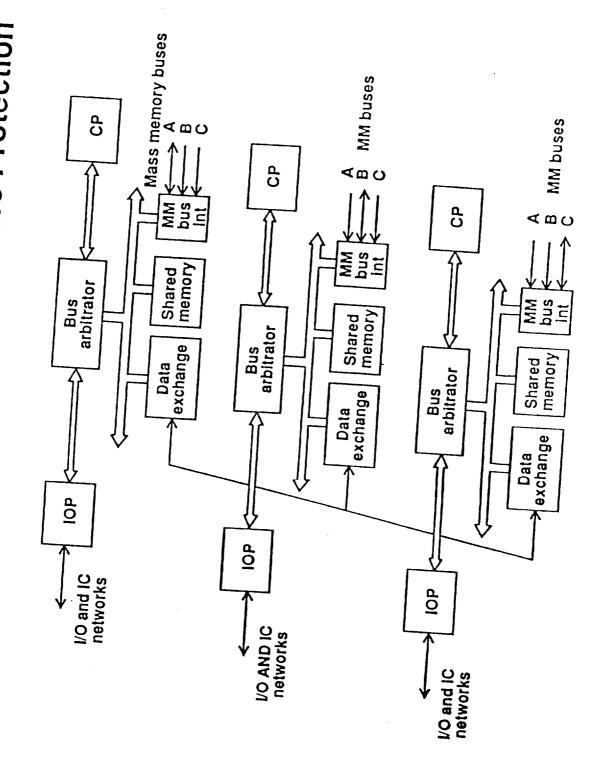

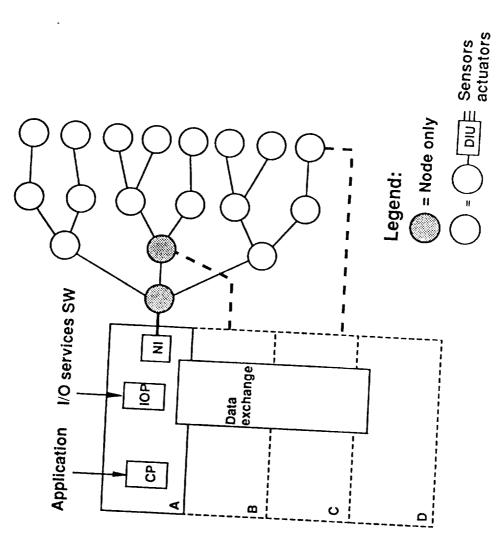

## Advanced Information Processing System

(AIPS)

Designed B y Charles Stark Draper Laboratory

Z 0/1 z z Z AIPS Proof-of-Concept Configuration 0/1 z z ADD-ON z FTP PROCESSOR (1) FTP (3) z z z 0/1 MULTIPRO-CESSOR Ŗ + Z z Z GATEWAY z z Π FТР (3) FТР (2) = TO ALL PROCESSORS z z z z z FROM: CSDL MASS 0/1 0/1

BOEING ADVANCED SYSTEMS

# FTP HW And SW Provide Failure Protection

C8158-C4.006-L7130 D4 ai

BOEING ADVANCED SYSTEMS

# Flight Control Computer With I/O Connections

C8224-04.001-L7130 D7

-

### Architecture

C0006-01.01 L7130 D34 Slide 18

# Reference Configuration Overview

~

# **Testing Experience**

- Application was quickly integrated into complex fault-tolerant AIPS system

- AIPS simplex application programming model

- CSDL staff assistance

- Impossible to meet goal of testing system with real time performance demands

- Slow time testing focused on system level interactions

- Nonintrusive measurements likely requirement for

- validation

- During real-time operation with full workload

- System services or operating system functions critical

- Not provided for in original AIPS testing/validation concept

### General Observations Architecture

### AIPS

C0008-01.01-L7130 D35ppS9

ž

### General Observations Architecture

Integrated flight control/propulsion control—feasible

- Obstacles—mind set problem

- Minimum use of sensors/activators

- Allows for optimum control

- Allows for function migration

- Growth potential

- Subset of Vehicle Management System

## General Observations (Cont) AIPS

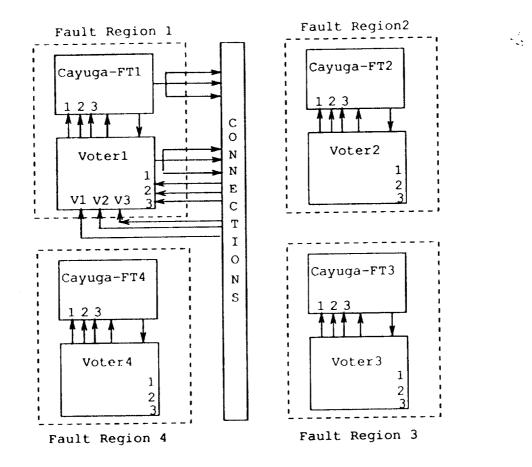

Very innovative for its time

- Supports true distributed system

- System redundancy transparent to user

- General set of building blocks-user selected

- Fault containment regions

C0006-05.01 L7130 D35 S1de 2

## General Observations (Cont) AIPS

- Advantages

- Building blocks allow expansion with minimum change

- Building block concept supports common

- hardware/software throughout the airplane

- Prevalidated building blocks for both hardware and

- Ability to mix elements with different reliability software

- requirements

- Distributed computing possible

- Minimizes maintenance and logistic issues Function migration possible

## General Observations (Cont) AIPS

- Advantages (cont)

- System redundancy is inherent in AIPS design

- Fault containment region is inherent in AIPS design

- Communications protocol allows design for minimum Pre-emptive priority allows application flexibility

- Concept supports dispatch with failures (need faster sensor/actuator time skew

- network repair time)

- Variation of components within FTP channel (CP/IOP or CP)

CC006-05.01 L7130 D35 Silde 4

## General Observations (Cont) AIPS

- Concepts needing attention

- Insufficient documentation

- IOP/Data Exchange bottleneck

- IC network traffic uncertain (not modeled)

- No discernable difference between network and bus for IAPSA requirements

## General Observations (Cont) AIPS

- Concepts needing attention (cont)

- Complex validation issues

- Resynchronization of channel during flight not possible with present design

- System design guidelines not established

- If IC modeled—it appears system would not work with present timing and loading requirements

C0006-05.01 L7130 D35 Slide 6

•

.

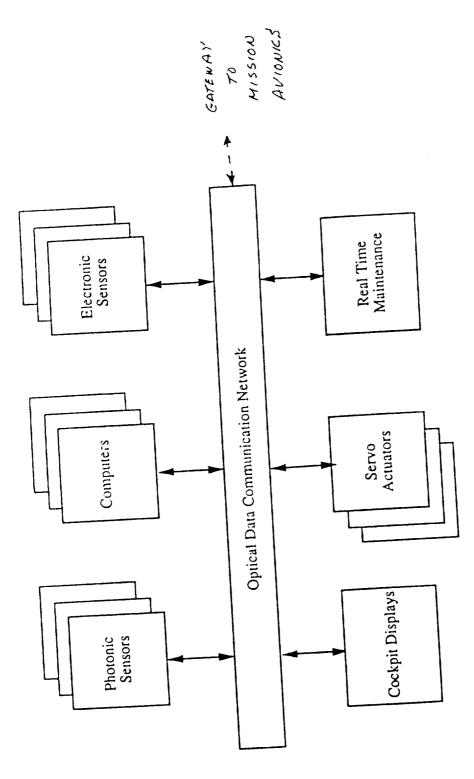

# Future Systems

.

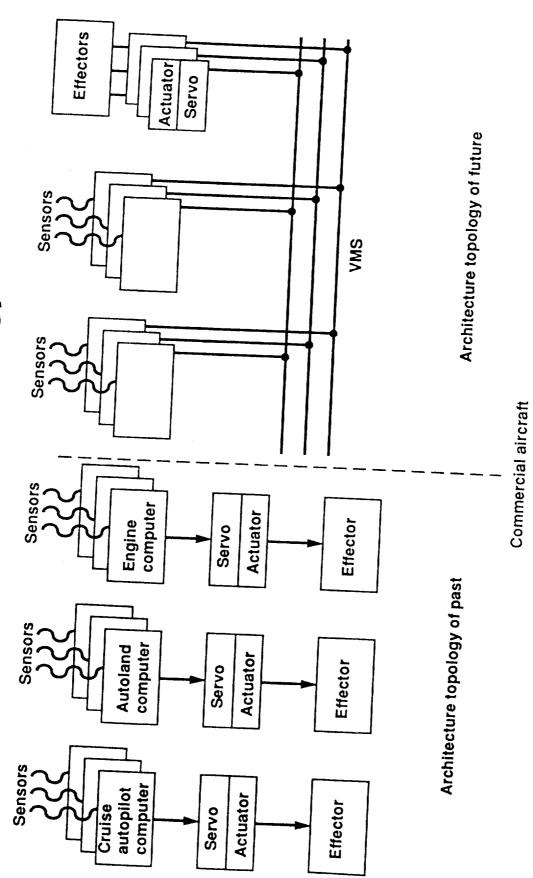

# Vehicle Management System

- All flight critical functions

- Failure causes loss of aircraft

- Near term military

- · Long term commercial

- ----

Generic VMS Architecture

## Photonics used for

- Bus

- Sensors

- I/0

- Actuators

- Computers (20 years)

•

## **Benefits of VMS**

- Performance

- Unified environment coordination of all tasks

- Growth capability

- Additional nodes minimum impact Life cycle replacement minimum topology

- impact

- Reliability

- Minimum set of building blocks

- Minimum part count Common I/O

- Sharing of sensor data

- Common redundancy management

ORIGINAL PAGE IS OF POOR QUALITY

ORIGINAL PAGE IS OF POOR QUALITY

# What does all this mean in terms of validation and verification?

- Design for validation is a critical technology

- Need indepth V&V concurrent with design analysis

# Solution to V&V

- Formal Verification viable solution to the V&V problem for

- Requirements/Specifications •

- Hardware •

- Software •

- System •

# Where are we in Formal Verification?

ŕ

the following 3 days should tell us!! 1

Č,

94 P-57 54-60

317685

### N91-17563 1

### MAFT:

### The Multicomputer Architecture for Fault-Tolerance

### R. M. KIECKHAFER

Computer Science and Engineering University of Nebraska – Lincoln Lincoln, NE 68588–0115 (402) 472–2402

rogerk@fergvax.unl.edu

MAFT is a product of the Allied-Signal Aerospace Company, Columbia MD.

UNL/CSE/RMK/August 14, 1990

NASA FM W-SHOP

### Abstract

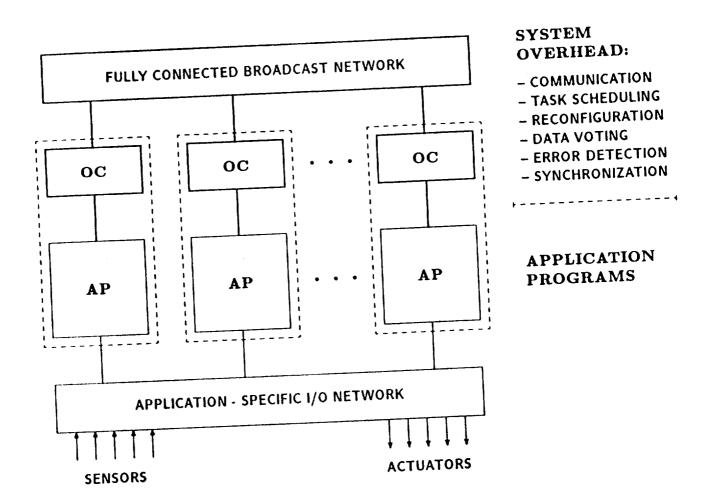

This presentation discusses several design decisions made and lessons learned in the design of the Multicomputer Architecture for Fault-Tolerance (MAFT). MAFT is a loosely coupled multiprocessor system designed to achieve an unreliability of less than  $10^{-10}/hr$  in flight-critical real-time applications.

The presentation begins with an overview of the MAFT design objectives and architecture. It then addresses the fault-tolerant implemention of major system functions in MAFT, including Communication, Task Scheduling, Reconfiguration, Clock Synchronization, Data Handling and Voting, and Error Handling and Recovery.

Special attention is given to the need for Byzantine Agreement or Approximate Agreement in various functions. Different methods were selected to achieve agreement in various subsystems. These methods are illustrated by a more detailed description of the Task Scheduling and Error Handling subsystems.

UNL/CSE/RMK/August 20, 1990

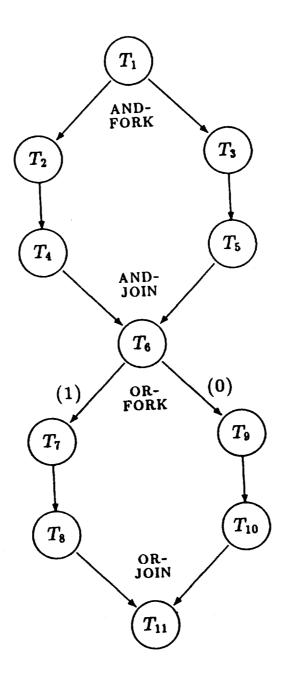

- INTRODUCTION

- SYSTEM FUNCTIONS

- Communication

- Task Scheduling

- Task Reconfiguration

- Clock Synchronization

- Data Handling and Voting

- Error Handling and Recovery

- SUMMARY

- RELIABILITY  $1.0 \times 10^{-9}$  over 10 hours.

- PERFORMANCE

- 200 Hz. Max Task Iteration Rate

5.5 MIPS Max Computational Capacity

1.0 MBPS Max I/O Transfer Rate

5.0 ms. Min Transport Lag (Input → Output)

- REUSABLE

- Functional Partitioning

- Application Specific Functions

- Standard Executive Functions

- LOW EXECUTIVE OVERHEAD

- Physical Partitioning

- · Separate Executive Processor

- · Hardware Intensive

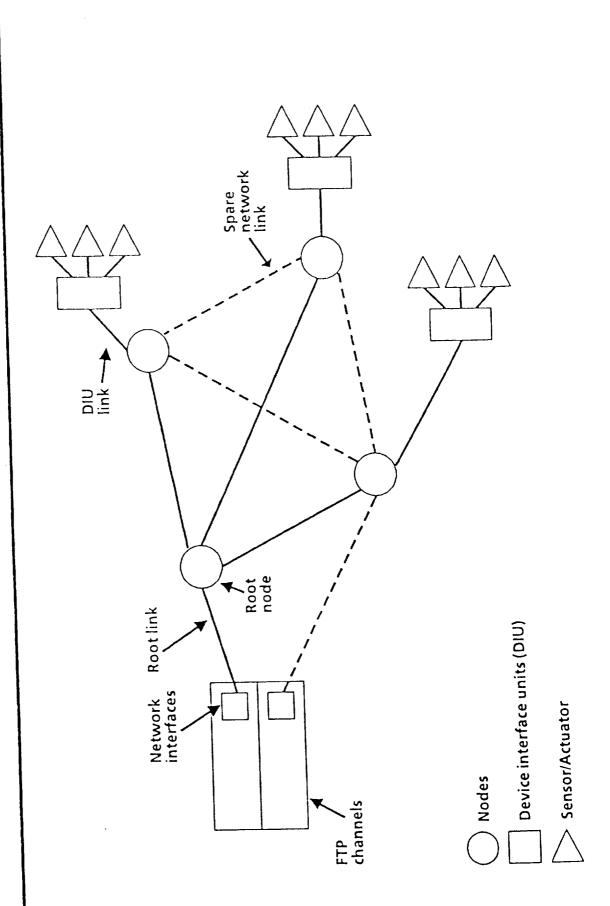

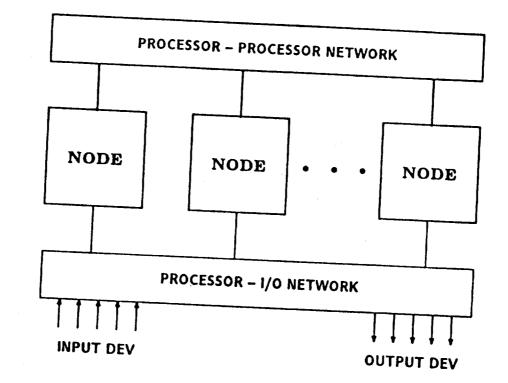

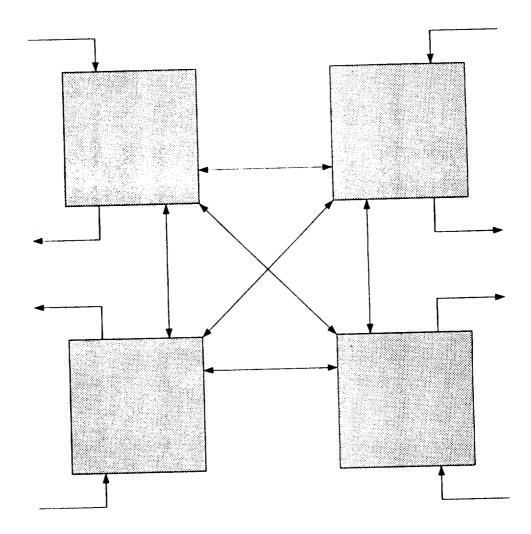

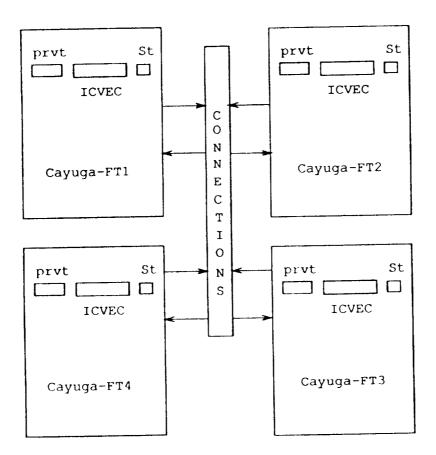

### Loosely-Coupled Multiprocessor

- Node ⇒ Processor and Private Memory

- No Shared Memory

.

Message-Based Inter-Node Communication

-21

5

Common Operating System

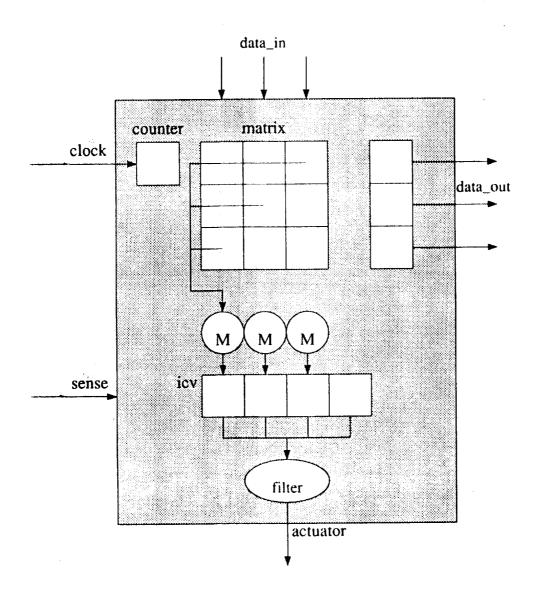

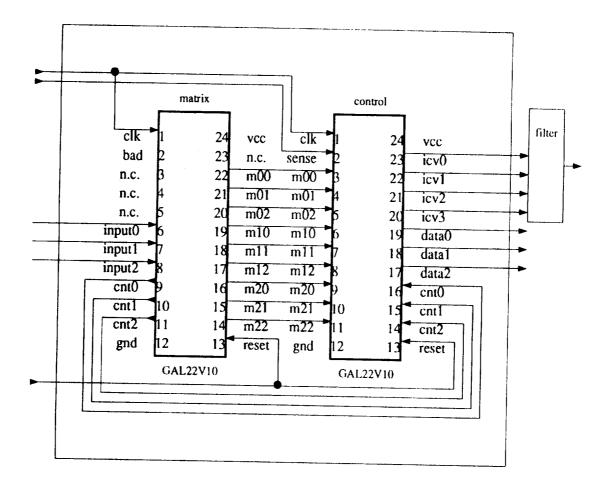

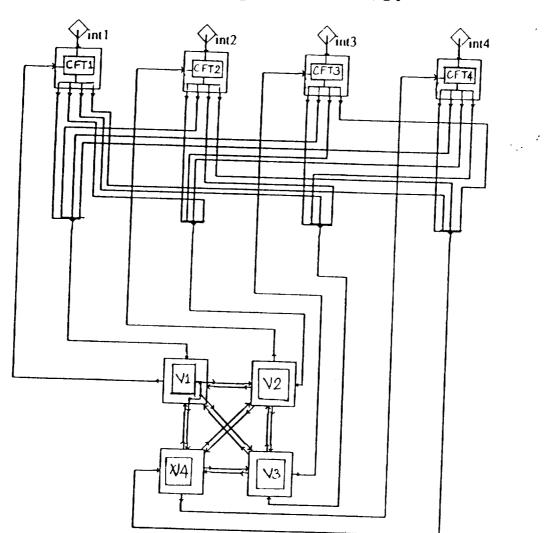

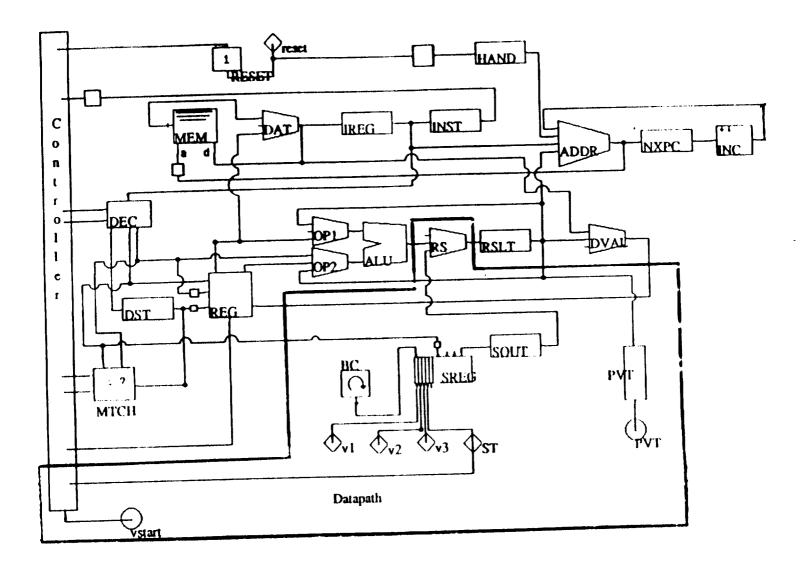

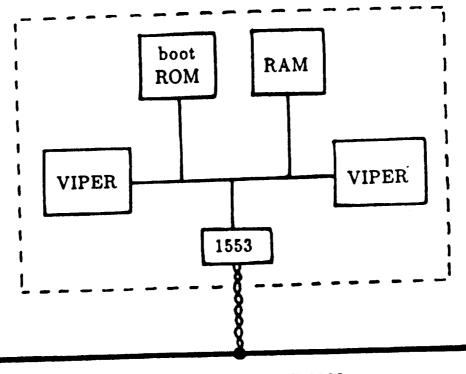

### MAFT System Architecture

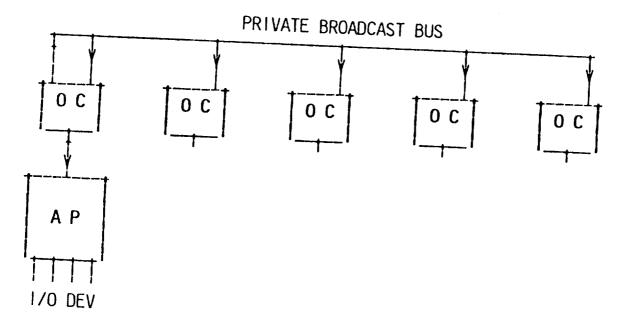

### • OC $\Rightarrow$ Operations Controller:

Special Purpose Device Common to All MAFT Systems

### • $AP \Rightarrow$ Application Processor:

General Purpose Application-Specific Processor.

UNL/CSE/RMK/August 15, 1990

NASA FM W-SHOP

### COMMUNICATION

UNL/CSE/RMK/August 16, 1989

12

CS-6

INTER-PROCESSOR COMMUNICATIONS

· ------

- INTRA-NETWORK COMMUNICATION

- MESSAGES TRANSMITTED ON PRIVATE SERIAL BROADCAST BUSSES

- ALL NODES RECEIVE, CHECK AND PROCESS ALL MESSAGES

- MESSAGE TYPES

- DATA (8/16/32B INT OR BOOL, IEEE STD 32B FLOAT)

- TASK COMPLETED / STARTED / BRANCH

- SYNCHRONIZATION / BRANCH INTERACTIVE CONSISTENCY

- ERROR REPORT

### - OC / AP COMMUNICATION

- 16 BIT ASYNCHRONOUS P.I.O. INTERFACE

- LOOKS LIKE "JUST ANOTHER 1/0 PORT" TO AP

- COMPATIBLE W/ EXISTING UNIPROCESSOR OPER SYST

FEBRUARY 28, 1986

Ś

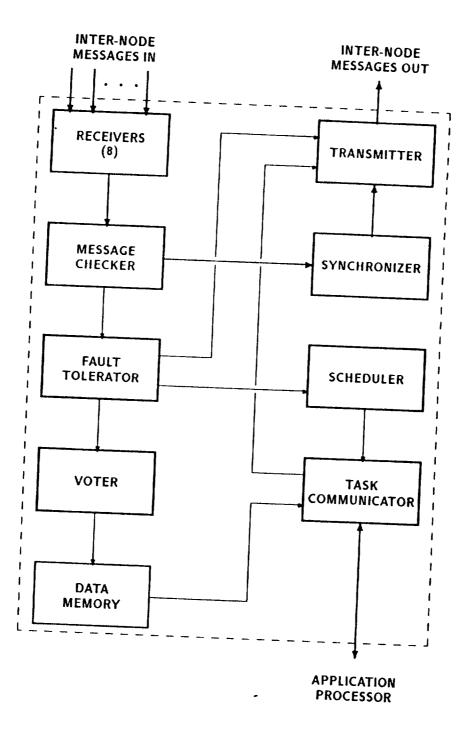

TRANSMITTER

- Format Msg NID, Msg Type, Framing, ECC

- Broadcast Msg

- RECEIVERS 1 per incoming link

- Accept Emperly Framed Bytes

- Buffer Byte for Message Checker

- MESSAGE CHECKER

- Poll Receivers 6.4  $\mu s$  cycle

- Physical and Logical Checks

- Steer Good Messages to Other Subsystems

- Dump Bad Messages into "Bit-Bucket"

### NASA FM W-SHOP

UNL/CSE/RMK/August 14, 1990

### LOCAL AP/OC INTERFACE OPERATIONS

\_\_\_\_

- 1. TASK SWITCHING PROCESS

- AP: DONE WITH LAST TASK, WHAT IS THE TASK IDENTIFICATION (TID) NUMBER OF THE NEXT TASK.

- OC: HERE IT IS

- 2. TRANSFER DATA FROM OC TO AP

- AP: GIVE ME THE NEXT INPUT DATA VALUE

- OC: HERE IT IS

- 3. TRANSFER DATA FROM AP TO OC

- AP: HERE'S THE NEXT OUTPUT DATA VALUE

-44

- OC: I GOT IT

+ ATC/RMK FEBRUARY 28, 1986

+

\_\_\_\_

.

### PERFORMANCE ISSUES

# • STRICTLY PERIODIC SCHEDULER

- Fast Freq Well Above Spec 500 Hz. vs. 200 Hz.

- Simple Binary Freq Dist  $(f_i = 2^{-i}f_0)$

- Flexible Conditional Branching

- Efficient Don't Keep AP Waiting

- NON-PREEMPTIVE

- Scheduler Complexity

- Context Switching Time Unknown Funct of AP

- High Frequencies Short Tasks

- NO OC INTERRUPTS I/O

- Scheduler Complexity

- Predictability

- High Frequencies Polling

- DMA or IOP access to AP Memory

- INTERNAL FUNCTION IS BLACK BOX

- VISIBLE PROPERTIES OF A TASK

- Priority (static, unique)

- Iteration Period

- Precedence Constraints

- Min and Max duration Limits

- Fixed Input and Output Shared Data Sets

- Branch Condition (asserted at completion)

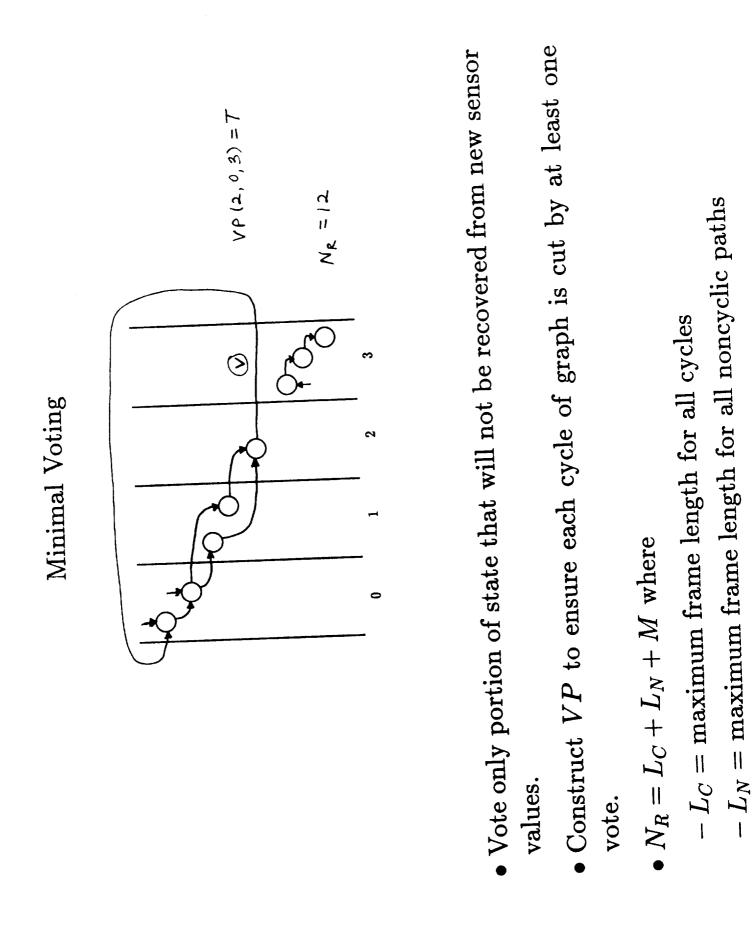

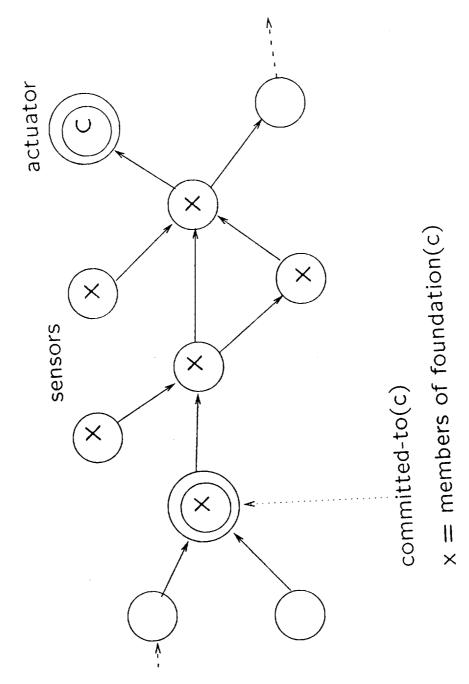

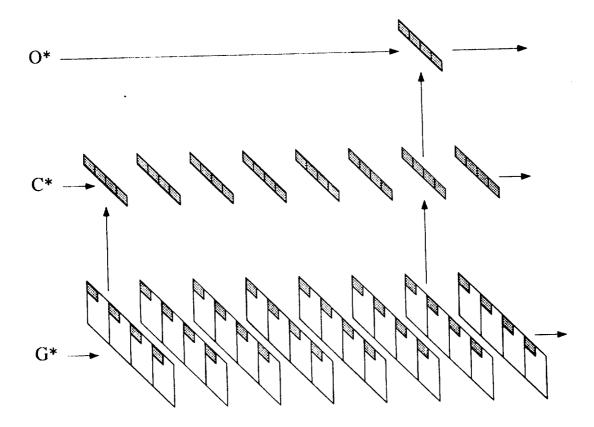

# FAULT-TOLERANCE ISSUES - I

- VARIABLE MODULAR REDUNDANCY

- Specify Redundancy of Each Individual Task

- Redundancy Matches Criticality

- No More Copies Than Necessary

- GLOBAL VERIFICATION

- Consensus Defines Correctness

- All Functions Observable and Predictable

- Replicated Global Scheduler

- Completed/Started (CS) Message:

- Node I.D.

- Started Task I.D.

- Branch Condition

- Delivery NOT GUARANTEED

- Single Msg Error Detect. NOT GUARANTEED - ECC coverage  $\geq (1 - 1 \times 10^{-6})$  per msg

- Repeated Undet. Errors PROBABILISTICALLY PRE-CLUDED

# TASK SCHEDULING

### FAULT-TOLERANCE ISSUES – II

### DISSIMILARITY BETWEEN COPIES

- Dissimilar Software and Hardware

- Guards Against Generic Faults

- No Guarantee Knight, Levenson, St. Jean

- Best Chance of Detecting Error

- Only Chance of Masking Error

- Implications

- Different Numerical Results

- Different Execution Times

- Impact on Scheduler

- Min and Max Execution Time Limits

10

- Vote on Branch Conditions in CS Messages

# FAULT-TOLERANCE ISSUES – III

# • BYZANTINE AGREEMENT

#### - Definition

- Agreement on All Messages

- Validity of Agreement

- Necessity in MAFT

- Consensus Defines Correctness

- Must Have Single Consensus

- Preconditions for Disagreement

- Initial Disagreement Enhanced by Dissimilarity

- Assymetric Communication Minimized by Busses

- Solution Interactive Consistency (Pease et al.)

- Global Receipt of All Messages

- Periodic Synchronized Re-Broadcast Rounds

- Vote on Received Re-Broadcasts

- Use Voted Values For All Scheduling Decisions

### IMPACT OF FAULT-TOLERANCE

- ALL COPIES DONE BEFORE SUCCESSORS RELEASED

- MAX EXECUTION TIMERS ASSURE PROGRESS

- CONFIRMATION DELAY MEAN 2.5 SUB.

- Only Affects Successors

- Efficiency Requires Parallel Paths

- FAULT-TOLERANCE LEVELS

- Single Asymmetric (Byzantine) Fault

- Double Symmetric Fault

- Reliability Modelling  $-10^{-10}/hr$  with 5 Nodes

# **MAFT Timing Hierarchy**

| PERIOD               | SPEC                         | DEFINITION                                   | BOUNDARY                           |

|----------------------|------------------------------|----------------------------------------------|------------------------------------|

| SUB-ATOMI            | C Min<br>400μ <i>s</i>       | I.C. Rebroadcast<br>Period<br>Min Guaranteed | Task Inter. Cons.<br>(TIC) Message |

|                      |                              | Task Duration                                |                                    |

| ΑΤΟΜΙϹ               | Min<br>2–2.8 <i>ms</i>       | Highest<br>Freq. Task                        | System State<br>(SS) Message       |

|                      |                              | Clock Sync.<br>Period                        |                                    |

| GENERAL<br>ITERATION | 2 <sup>i</sup><br>Atom. Per. | Intermed.<br>Freq.Tasks                      | System State<br>(SS) Message       |

| MASTER               | Max 1 <i>K</i><br>Atom. Per. | Lowest<br>Freq. Task                         | System State<br>(SS) Message       |

UNL/CSE/RMK/August 15, 1990

8

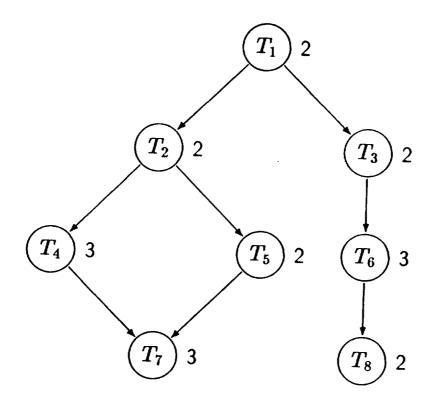

- SCHEDULING INSTABILITY Anomalous or unpredictable variations in total execution time (Makespan) due to variations in system parameters.

- MULTIPROCESSOR ANOMALIES Observation that Makespan can be *increased* by:

- Increasing Number of Processors,

- Relaxing Precedence Constraints,

- Decreasing Individual Task Durations.

- DYNAMIC FAILURE Condition where all tasks execute properly *except* that deadlines are missed.

- Can occur in a fault-free system,

- Can be induced by instability.

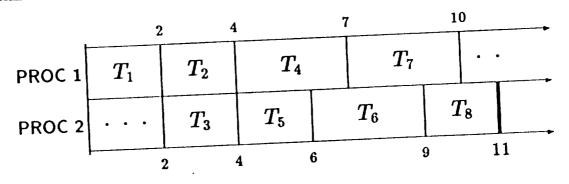

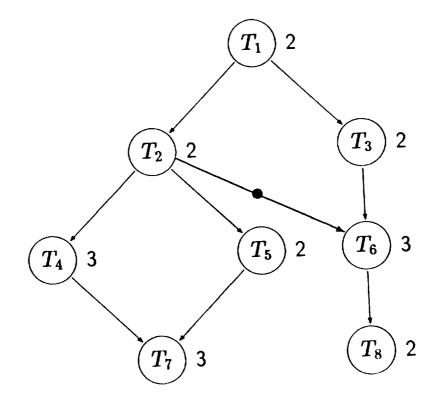

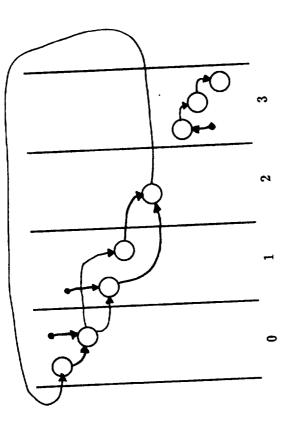

STANDARD GANTT CHART (max task durations)

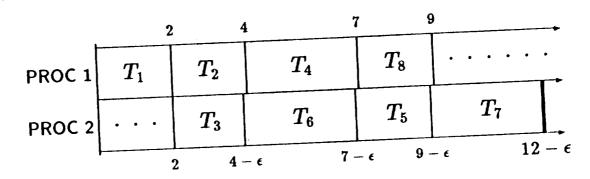

• NON-STANDARD GANTT CHART (shorten  $T_3$  by  $\epsilon$ )

WHAT HAPPENED?

- $T_3$  finished before  $T_2$ ,

- $T_6$  "ready" before  $T_5$ ,

- $T_5$  displaced by  $T_6 \Rightarrow$  Priority Inversion,

- Critical path  $(T_2

ightarrow T_7)$  impeded.

• GRAHAM (1969) – Bound Magnitude of Instability

$$rac{\omega'}{\omega}=2-rac{1}{N}$$

- $\omega$  = Makespan of Standard Gantt Chart,

- $\omega' =$  Makespan of worst-case schedule,

- N = Number of Processors.

- MANACHER (1967) Stabilization Algorithm

- Necessary Pre-conditions

- i. ∃ "fork" in Precedence Graph,

- ii. Successors of forking task run in parallel on Standard Gantt Chart,

- iii. Possible priority inversion around fork.

- Solution Impose Artificial Dependency around fork.

• MANACHER ARTIFICIAL DEPENDENCY  $(T_2 \rightarrow T_6)$

• EFFECT

- $T_2$  is common parent for both  $T_5$  and  $T_6$ ,

- $T_6$  will be "ready" no earlier than  $T_5$ ,

- $T_5$  precedes  $T_6$  in priority list,

- $T_6$  can not be selected before  $T_5$ .

- Sufficient, but not always necessary

- Adds Scheduling Overhead (resolve edge)

- Unrealistic System Model

- Assumes no scheduler overhead,

- Assumes dynamic allocation,

- Allows for no Confirmation Delay,

- Ignores minimum duration bounds,

- Does not predict magnitude of instability.

- Find Necessary and Sufficient Stability Conditions.

- Develop Stabilization Strategies

- Task System Stabilization

- Edge Stabilization (Manacher)

- · Vertex Stabilization

- Hybrid Stabilization

- Run-Time Scheduler Stabilization

- · Limited Scan Depth

- Scheduling Algorithm Stabilization

- · Sched. Algorithm Assigns Priorities

- · Constrain to Preclude Necessary Conditions

- Extend System Environment

- Scheduler Overhead

- Static Allocation

- Confirmation Delay

- Minimum Duration Bounds

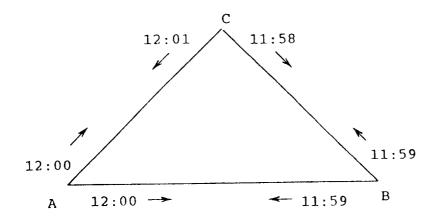

# SYNCHRONIZATION

X

- Periodically Exchange System State (SS) Msgs

- SS Msg  $\Rightarrow$  "Atomic Period" Boundary

- Synchronization Period = 2 Atomic Periods

- Loosely Synchronized Individual Clocks

- Msg Exchange  $\Rightarrow$  No Separate Clock Lines

- Physical Separation  $\Rightarrow$  Damage Tolerance

- Robustness to "Common Upset" events

- Synchronization Modes

- Steady State Maintain Existing Synchronization

- Warm Start Converge to Existing Operating Set

- Cold Start Form Initial Operating Set

- Interactive Convergence to synchronize

- $\cdot$  Interactive Consistency  $\Rightarrow$  Steady State

- · Origin of Two-phase algorithm

# DATA HANDLING AND VOTING

K

\_ \_

UNL/CSE/RMK/August 16, 1989

٠

- $\epsilon = 7 \ \mu sec 600$  ft. separation

- $ho=5\cdot10^{-5}$

- $R = 20 \ msec \Rightarrow 10 \ msec$  Atomic Pd.  $\Rightarrow 100 \ Hz$ .

- $\rho R = 1 \ \mu sec$

- No Faults: Max  $\delta = 8.5 \mu \ sec$

- With Faults: Max  $\delta = 16.5 \mu \; sec$

### Data Management

- DATA GENERATED BY AP

- BROADCAST IN DATA MESSAGE

- RECEIVED AND PROCESSED BY ALL NDOES

- Static Limit Check

- On-The-Fly Vote

- Dynamic Deviance Check

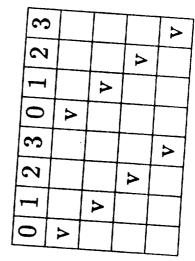

### On-The-Fly Voting I

- TRIGGERED BY DATA MESSAGE ARRIVAL

- DATA ID ACTS AS UNIQUE VARIABLE NAME

- USE ALL PREVIOUS COPIES OF SAME DATA ID

- MS or MME (programmer selectable)

- Sort Serially High-Order-Bit First

- · Select 2 "Medial" Values

- Average (Add and Shift)

- No I.C. Vote for Boolean Types

- · Difficult to implelement round 2

- · Usually Control Data for Mode Switch

- ∃ Better Way for Mode Switch

### • DEVIANCE CHECK

- Compare Each Copy to Voted Value

- Excessive Difference  $\Rightarrow$  error

- Programmer Sets Limits

- Generate Error Vector  $\Rightarrow$  Source Nodes

### • TERMINATE

- Scheduler Says All Copies Done

- Send Error Vector to Fault-Tolerator

- Send Voted Value to Data Memory

- Swap On-line/Off-line Buffers in Data Memory

- Clear Previously Received Copies from Voter

# ERROR HANDLING AND RECOCVERY

UNL/CSE/RMK/August 16, 1989

1

CS-990

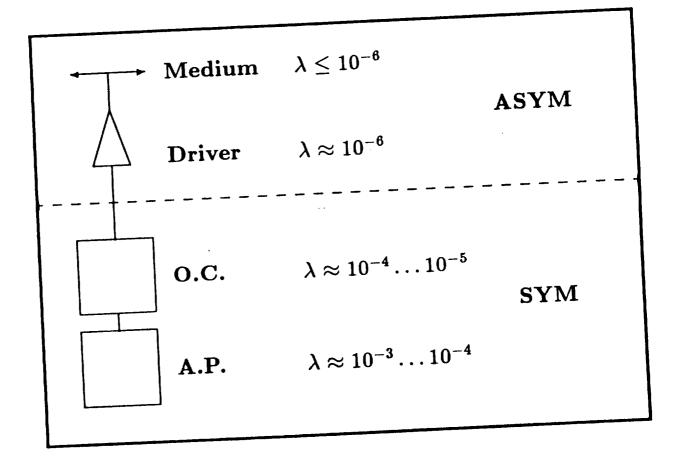

• BYZANTINE (MALICIOUS)

Pease et al. (1982)

- $N \ge 3t + 1$

- $r \geq t$

- MALICIOUS U BENIGN (self-evident)

Meyer and Pradhan (1987)

• (ASYMMETRIC U SYMMETRIC) U BENIGN

Thambidurai and Park (1989)

$$t = a + s + b$$

-  $N \ge 3a + 2s + b + r + 1$

-  $r \ge a$

UNL/CSE/RMK/August 17, 1990

NASA FM W-SHOP

• Can Estimate Separate  $\lambda$ 's

-

$$\lambda_{asym} \approx 10^{-6}$$

-  $\lambda_{sym} \approx 10^{-3} \dots 10^{-4}$

• Generic Fault = Multiple Symmetric

-

$$\lambda_{gen} \approx 10^{-5}$$

?

NASA FM W-SHO

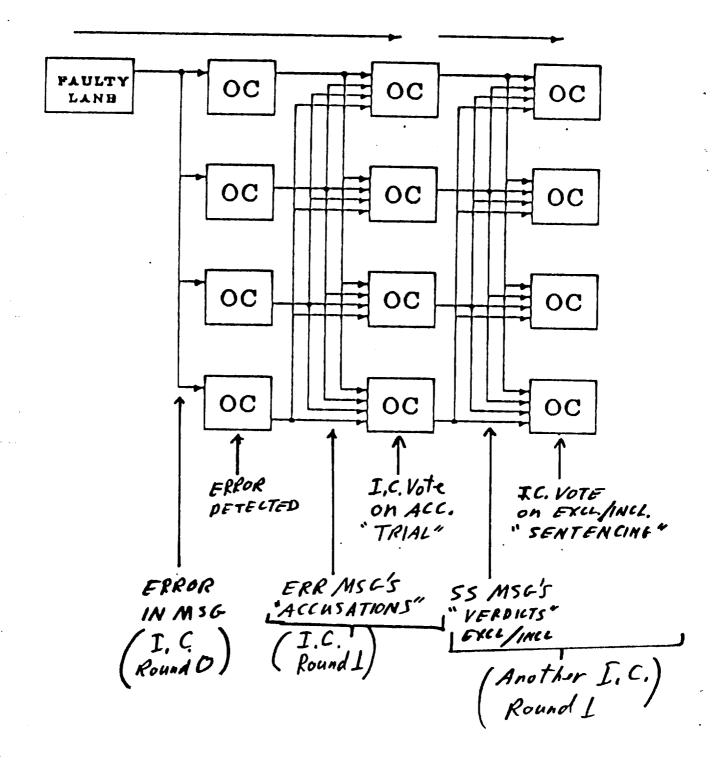

- Errors Are Manifested In Messages

- Physical: ECC, framing, length

- Contents: values

- Timing or sequencing

- Existence or non-existence

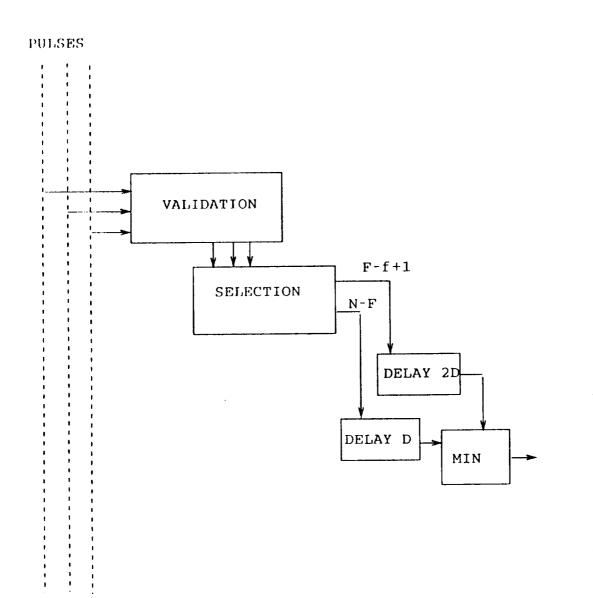

- Log Errors Over One Atomic Period

- Errors reported by all subsystems

- Fault-Tolerator records errors

- -∃ 31 separate error "flags"

- $\exists$  Unique "Penalty Weight" PW for each flag

- $\exists$  "Incremental Penalty Count" *IPC* for each node

- FOR each flag f reported against node i:

- $\cdot IPC(i) := IPC(i) + PW(f)$

- Broadcast ERR(i) Message

- At beginning of next Atomic Period

- Contents:

- $\cdot IPC(i)$

- $\cdot BPC(i)$  Base (current) penalty count

- $\cdot$  All Error Flags for node i

- No ERR Message  $\Rightarrow$  No Detections

- BPC  $\Rightarrow$  Health Of Node

- Increasing BPC ERR Message Vote

- Vote on BPC(i)

- Vote on IPC(i)

- BPC(i) := BPC(i) + IPC(i)

- Decreasing BPC Fixed decrement

- $\exists$  Penalty Decrement value PD

- At New Master Period

- -BPC(\*) := BPC(\*) PD

- Allows For Eventual Readmission

CS-990

4

- Recommend Exclusion/Readmission

- $\exists$  Exclusion Threshold  $T_{excl}$

- $\exists$  Admission Threshold  $T_{adm}$

- Recommend in next SS message:

- $\cdot BPC(i) \geq T_{excl} \Rightarrow \mathsf{Exclude} i$

- $\cdot BPC(i) \leq T_{adm} \Rightarrow \text{Readmit } i$

- $T_{adm} < BPC(i) < T_{excl} \Rightarrow$  No Change

- I.C. Vote on Recommendations

- Consistent System State is Critical

- Free (needed for cold-start)

- Highly Degraded Systems

- Common Mode Upset Recovery

time

ERROR HANDLING (SIMPLEX I.C.)

- AP Diagnostics in Workload

- OC System Level Self-Test

- Errors Very Rare

- Inject Faults to Excercise Error Detection

- · Special self-test Task ID

- · Suspend normal Transmitter Ops

- Tranmsit string from self-test ROM

- · Can transmit ANY test scenario

- Test Results Based On

- · False/Missed Accusations

- · Cyclic Link Check

- Independent of Actual Bit-Stream

- Rotate "Originator" Duty

- Complete Coverage If ANY One Node Correct

# Version Management

- SSV = System State Vec eg (2,1,1)

- VMV = Version Management Vec eg (1,1,1)

- WMV = Workload Management Vec (SSV) or (VMV)

- Vectors Used By Different Subsystems

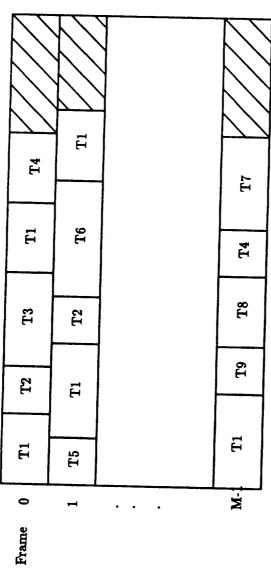

Data VoterVMVInactive Copy Ignored For VoteDev CheckerSSVInactive Copy Still MonitoredSchedulerWMVInactive Copy May Not Run

- WMV = SSV

- Inactive Copy Still Executing

- Actual Tasks Being Monitored

- Best for Generic Fault Detection

- WMV = VMV

- Inactive Copy Doing Something Else

- Will Not Be Affected By Generic

- Can Activate To Replace Sibling

- Best For Generic Recovery

- MAFT error detection is by consensus

- Each node reports errors on all nodes.

- Majority vote confirms or denies accusations.

- Disagreement with majority may itself be an error.

- Faulty node must be detected by majority of nodes

- Must be "far enough" out of sync

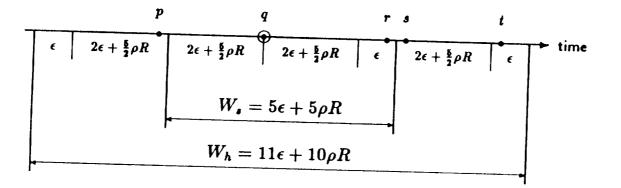

- There exists a region of ambiguity

- Defines size of "Sync Window"

- $W_s = \text{SOFT ERROR WINDOW}$

- Spans Range of Receipts from Non-Faulty Nodes

- Error May Not Be Confirmed

- Inherent Ambiguity

- Must Suspend Error Disagreement Penalties

- $W_h = HARD ERROR WINDOW$

- IF Any non-faulty node detects a Hard-Error THEN All non-faulty nodes detect an Error

- Can demand Corroboration

- $\epsilon = 7 \ \mu sec 600$  ft. separation

- $ho=5\cdot10^{-5}$

- $R = 20 \ msec \Rightarrow 10 \ msec$  Atomic Pd.  $\Rightarrow 100 \ Hz$ .

•

$$\rho R = 1 \ \mu sec$$

- No Faults: Max  $\delta = 8.5 \mu$  sec

- With Faults: Max  $\delta = 16.5 \mu$  sec

•

$$W_s = 40\mu \ sec$$

•  $W_h = 87\mu \ sec$

UNL/CSE/RMK/August 16, 1990

## SUMMARY

UNL/CSE/RMK/August 16, 1989

SUMMARY COMMENTS ON THE APPLICATION OF MAFT TECHNOLOGY

## 1. CAPABILITIES

----

- BASIS OF A GENERIC REAL-TIME MULTICOMPUTER SYSTEM

- REMOVES F.T. OVERHEAD FROM APPLICATION PROCESSOR

- HANDLES ALL REDUNDANCY MANAGEMENT WITHIN COMPUTER

- ASSISTS IN REDUNDANCY MANAGEMENT OF 1/0 SYSTEM

### 2. FLEXIBILITY

- INDEPENDENT OF I/O ARCHITECTURE

- HIGHLY RECONFIGURABLE AND GRACEFULLY DEGRADABLE

- PROVIDES MECHANISMS, NOT POLICIES

### 3. USABILITY

## ADVANTAGES OF APPROACH

- PARTITIONED APPROACH SIGNIFICANTLY REDUCES PROCESSOR OVERHEAD

- DATA DRIVEN ARCHITECTURE MUCH FASTER THAN SOFTWARE IMPLEMENTATION

- NOT DEPENDENT UPON ARCHITECTURE OF APPLICATION PROCESSOR

- REDUNDANCY IS "TASK-BASED" AND FLEXIBLE

- SUITABLE FOR HIGH RELIABILITY AND HIGH PERFORMANCE APPLICATIONS

## MAFT Bibliography

## References

.

| [Dar88]   | Darwiche, A.A., and F.M. Doerenberg, "Application of the Bendix/King Multicom-<br>puter Architecture for Fault-Tolerance in a Digital Fly-By-Wire Control System", <i>Mid-</i><br>con, Aug 1988. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [Glu86]   | Gluch, D.P., and M.J. Paul, "Fault-Tolerance in Distributed Digital Fly-by-Wire<br>Flight Control Systems", AIAA/IEEE Seventh Digital Avionics Systems Conference,<br>Oct 1986.                  |

| [Kie87]   | Kieckhafer, R.M., "Task Reconfiguration in a Distributed Real-Time System," Eighth<br>IEEE Real-Time Systems Symposium, Dec 1987.                                                                |

| [Kie88]   | Kieckhafer, R.M., et al, "The MAFT Architecture for Distributed Fault-Tolerance",<br>IEEE Trans. Computers, V. C-37, No. 4, pp. 398-405, Apr 1988.                                               |

| [Kie89]   | Kieckhafer, R.M., "Fault-Tolerant Real-Time Task Scheduling in the MAFT Dis-<br>tributed System," Proc, Twenty-Second Hawaii International Conference on System<br>Sciences, Jan 1989.           |

| [McE88]   | McElvany, M.C., "Guaranteeing Deadlines in MAFT," Proc. IEEE Real-Time Systems<br>Symp., pp. 130-139, Dec 1988.                                                                                  |

| [Tha88]   | Thambidurai, P.M., and Y.K. Park, "Interactive Consistency with Multiple Failure<br>Modes", Proc. Seventh Reliable Dist Systems Symp., Oct 1988.                                                 |

| ['Tha88a] | Thambidurai, P.M. Critical Issues in the Design of Distributed, Fault-Tolerant, Hard<br>Real-Time Systems, Ph.D. Dissertation, Dept. of Electrical Engineering, Duke Univer-<br>sity, 1988.      |

| [Tha89]   | Thambidurai, P.M., et al., "Clock Synchronization in MAFT", Nineteenth Fault-<br>Tolerant Computing Symposium, pp. 142-151, Jun 1989.                                                            |

| [Wal88]   | C.J. Walter, "MAFT: An Architecture for Reliable Fly-by-Wire Flight Control," Proc.<br>AIAA/IEEE Eighth Digital Avionics Systems Conference, pp. 415-421, Oct 1988.                              |

35-61 P19 いたってい 146

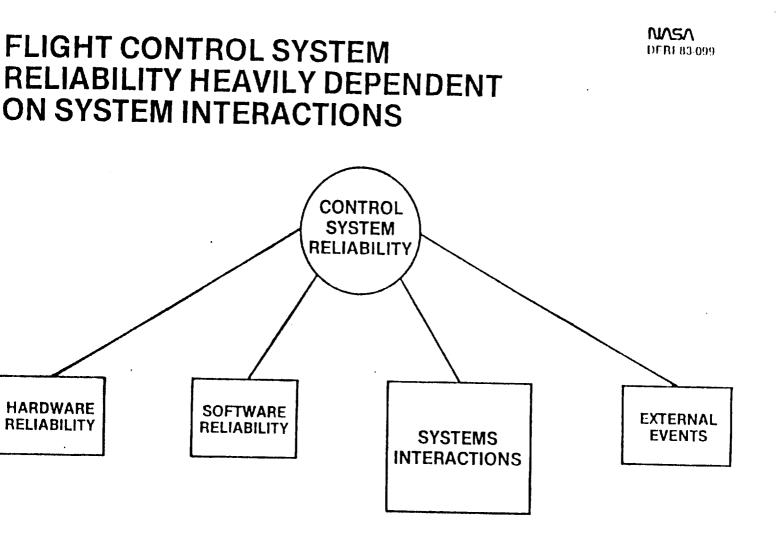

Design For Validation Based on Formal Methods

Ricky W. Butler

NASA Langley Research Center Hampton, VA 23665 N91-17564

# VALIDATION OF ULTRA-RELIABLE SYSTEMS

DECOMPOSES INTO TWO SUBPROBLEMS

1. Quantification of probability of system failure due to physical failure

2. Establishing that **DESIGN ERRORS** are not present<sup>1</sup>.

$^{1}(note. Quantification of 2 is infeasible)$

## Achieving Ultra-Reliable Software (Approaches)

- Testing (Lots of it)

- Design Diversity (e.g. N-version programming)

- Fault Avoidance:

- Formal Specification/Verification

- Automatic Program Synthesis

- Reusable Modules

## Life-Testing

Basic Observation:

$10^{-9}$  Probability of failure estimate for a 1 hour mission

REQUIRES

$> 10^9$  hours of testing

$(10^9 \text{ hours} = 114,000 \text{ years})$

## Design Diversity

- 1. Separate Design/Implementation Teams

- 2. Same Specification

- 3. Multiple Versions

- 4. Non-exact Threshold Voters

5. Hope design flaws manifest errors independently or nearly so.

!

•

The Big Problem For Design Diversity Advocates

- experiments in the low-nominal reliability region have shown that the number of near-coincident failures far exceeds the number predicted by an independence model.

- Certainly independence cannot be assumed axiomatically for ultrareliable regime

- If cannot assume independence must measure correlations.

Quantification of N-version programs not feasible in the ultrareliable

regime

- Since one cannot assume independence, it must be treated as black box

- Back to life-testing problem again

- Any alternative model would have to be validated. But How?

| THE DEMONSTRAT             |

|----------------------------|

| INDEPENDENCE ASSUMPTION !! |

|                            |

- THE INDEPENDENCE ASSUMPTION CANNOT BE DEMONS FOR MULTI-VERSION S/W IN THE ULTRA-RELIABLE RE-GION The Danger of Design Diversity (N-version Programming, Recovery Blocks, etc.)

- dence, the advocators of S/W fault-tolerance generate ultra-high creates an "illusion" of ultra-reliability. By assuming indepenestimates of reliability.

- As long as industry/certification agencies believe that S/W faulttolerance will solve the problem, formal methods will not be pursued. 1

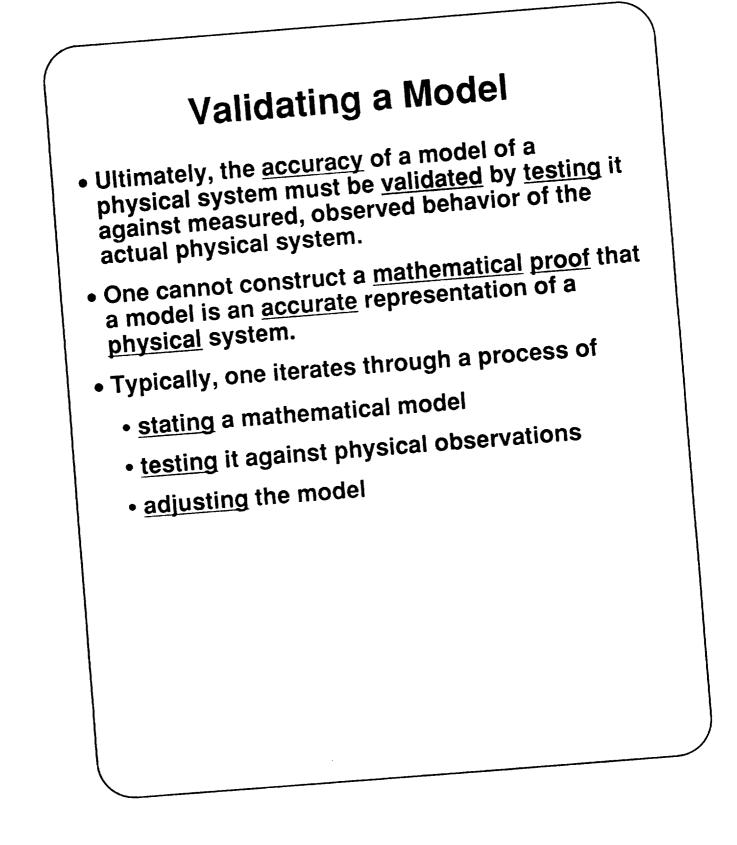

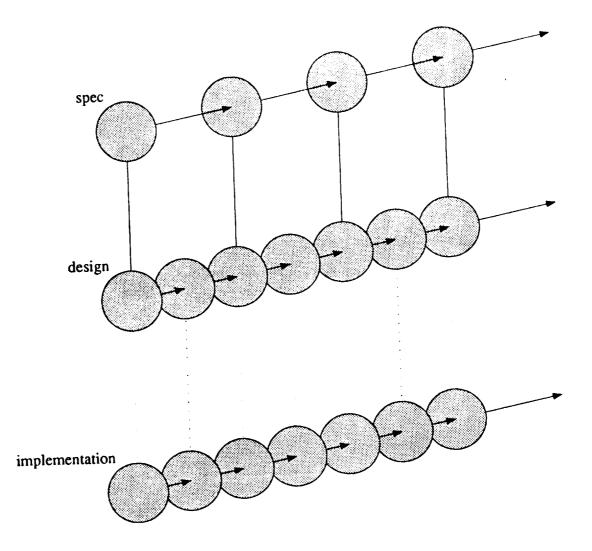

# Design For Validation

- 1. Designing a system in a manner that a complete and accurate reliability model can be must be measured. All such parameters must be measurable within a feasible amount of constructed. All parameters of the model which cannot be deduced from the logical design time.

- performance properties yet requires the measurement of hundreds of parameters (e.g say by time-consuming fault-injection experiments) would be rejected over a less capable system surable parameters in order to reduce the validation cost. A design which has exceptional 2. The design process makes tradeoffs in favor of designs which minimize the number of meathat requires minimal expermimentation.

- 3. The system is designed in a manner that enables a proof of correctness of its logical structure. Thus, the reliability model does not include transitions representing design errors.

- 4. The reliability model is shown to be accurate with respect to the system implementation. This is accomplished analytically.

| ustration |

|-----------|

|           |

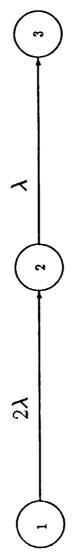

Suppose we must design a simple fault-tolerant system with a probability of failure no greater than  $2 \times 10^{-6}$  whose maximum mission time is 10 hours.

- We quickly eliminate the use of a simplex processor since there is no technology which can produce a processor with this low of a failure rate.

- Thus, we begin to explore the notion of fault-tolerance. We next consider the use of redundancy-how about a dual? When the first processor fails, we will automatically switch to the other processor.

Unfortunately, our design suffers from one major problem. It is **impossible** to *prove* that any implementation behaves in accordance with this model. The problem is that one cannot design a dual system which can detect the failure of the first processor and switch to the second 100% of the time. Thus, we must accept the fact that there is a single-point failure in our system an include it in our reliability model

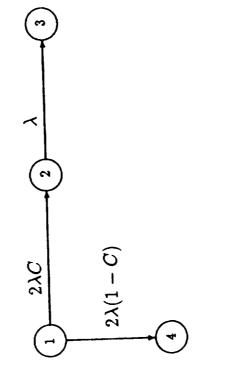

## SURE Run

Now we have a parameter in our model which must be measured—C. It represents the fraction of single faults from which the system successfully recovers. Can this parameter can be measured in a feasible amount of time (i.e. say less than year) with statistical significance?

## \$ sure

SURE V7.5 MASA Langley Research Center

17 read dualspf 2:

|                                                                                       | RB0        | ٠           | -           | 1.609200-04 | 1.40930-04  | Ĩ           | 1.009508-04 | -           | -00700. | 4.098000-05 | •       |           | •           |

|---------------------------------------------------------------------------------------|------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|---------|-------------|---------|-----------|-------------|

| = 1E-4;<br>TO 1 BY 0.01;<br>+LAMBDA+C;<br>AMBDA:<br>+(1-C)+LAMBDA;                    | LOVERBOUND | 2.00699e-04 | 1.80729e-04 | 1.60759e-04 | 1.407890-04 | 1.208190-04 | 1.00849e-04 | 8.08790e-05 | •       | -093906-    | -006960 |           |             |

| 2: LAMBDA =<br>4: C = .9 TO<br>5: 1,2 = 2*L<br>6: 2,3 = LAM<br>7: 1,4 = 2*(<br>8? run | υ          | Ē           | -00001      | •           |             | •           | •           | •           | •       |             |         | 0-20000e. | 1.000000+00 |

From this run we know that C must be between 9.9 and 1.0 in order to meet our reliability goal. We rerun the model to get a closer value:

## 2nd Run

## \$ sure

9? read dualspf

LAMBDA = 1E-4; C = .999 T0 1 BY 0.0001; 1.2 = 2\*LAMBDA\*C; 10040 101

2,3 = LAMBDA; 1,4 = 2\*(1-C)\*LAMBDA;

0.02 SECS. TO READ MODEL FILE 16? run

RUN #2 COMMENTS UPPERBOUND 2.99900e-06 2.79910e-06 .39930e-06 .999500-06 .59920-06 2.19940e-06 1.79960e-06 . 59970e-06 .39980-06 .19990e-06 1.00000-06 LOWERBOUND 2.99600e-06 2.79630e-06 2.39690e-06 2.19720e-06 1.997500-06 .79780e-06 .59810e-06 2.59660e-06 .39840e-06 .19870e-06 9.990008-07 9.99100-01 9.99200-01 9.99300-01 9.99400-01 9.99500-01 9.99500-01 9.99800-01 9.99800-01 9.99800-01 9.99800-01 .990006-01 1.00000+00 υ

• Now, we can see that we must demonstrate that C is greater than 0.9995.

• it can shown that 20000 observations are necessary to estimate this parameter to a reasonable level of statistical significance.

• If we optimistically assume that each fault injection requires 1 minute, then this validation exercise would require 330 hours (i.e. 14 days).

In this case, we decide we can live with this amount of testing and proceed to develop our system.

÷ į

; į

: . .

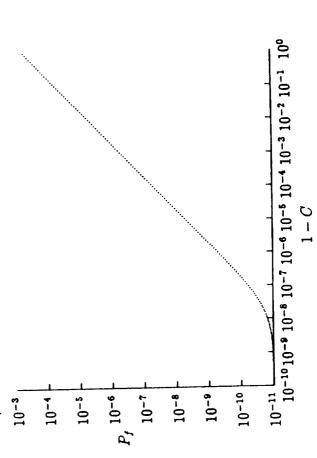

Designing System with Much Higher Reliability

Now suppose we want to meet the reliability goal of  $1 - 10^{-9}$ .

We decide to use a nonreconfigurable 5-plex (5MR) and build a processor with a failure rate of  $10^{-5}/hour$ . The probability of system failure is plotted as a function of 1-C:

- The value of C must now be greater than 0.9999982.

- It can be shown that over a million fault injections would be required to measure this parameter even if we are very optimistic about the testing process

- If each injection required 1 minute, this would require almost 1.9 years of non-stop fault injections.

A better Way—via Design For Validation

It would be nice if we could design our system so that such an experiment is unnecessary.

- The system is designed so that a single point failure **cannot** cause system failure (i.e. C = 1).

- This is demonstrated to be true by formal proof. 1

- Thus, one uses the power of analysis to eliminate fault-injection style testing. I

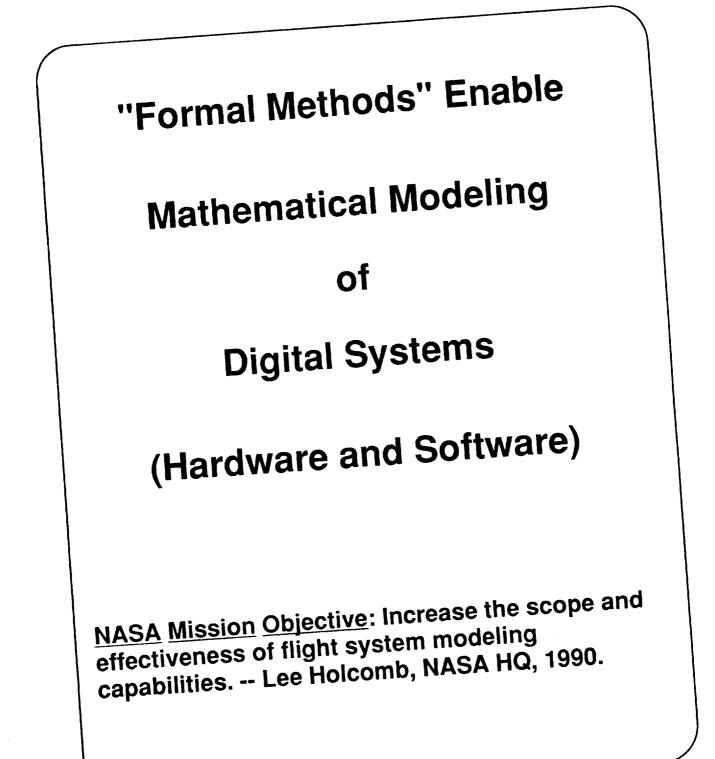

# WHY FORMAL METHODS?

The successful engineering of complex computing systems will require the application of mathematically based analysis analogous to the structural analysis performed before a bridge or airplane wing is built.

# Draft Interim Defence Standard 00-55

Quote from the foreward to the Draft Standard:

the long-term, become cumbersome and inefficient for the assurance The Steering Group "has determined that the current approach which is based on system testing and oversight of the design process will, in of the safety of increasingly sophisticated software". "The Steering Group therefore proposes the adoption of Formal Design Methods, based on rigorous mathematical principles, for the implementation of safety-critical computer software". Levels of Formal Methods

Static Code Analysis (i.e. no semantic analysis) Level 0:

Level 1: Specification using mathematical logic or language with a formal semantics (i.e. meaning expressible in logic)

Formal Specification + Hand Proofs Level 2:

Formal Specification + Mechanical Proofs Level 3:

## Summary

- Testing and design-diversity techniques inadequate.

- A design-for-validation based on formal methods is needed for the digital flight control systems problem.

- Formal methods will play a major role in the development of future high reliability digital systems. 1

## What FM can offer DFCS Design

John Rushby

Computer Science Laboratory SRI International

## Overview

-----

- What has actually gone wrong in practice?

- What is the pattern?

- What is the solution?

## Advanced Fighter Technology Integration (AFTI) F16

- Triplex DFCS to provide two-fail operative design

- Analog backup

- Digital computers were not synchronized

- "General Dynamics believed synchronization would introduce a single-point failure caused by EMI and lightning effects"

## AFTI F16 DFCS Redundancy Management

- Each computer samples sensors independently, uses average of the good channels, with wide threshold

- Single output channel selected from among the good channels

- Output threshold 15% plus rate of change

- Four bad values in a row and the channel is voted out

## AFTI F16 Flight Test, Flight 15

- Stores Management System (SMS) relays pilot requests for mode changes to DFCS

- An unknown failure in the SMS caused it to request mode changes 50 times a second

- DFCS responded at a rate of 5 mode changes per second

- Pilot said aircraft felt like it was in turbulence

- Analysis showed that if aircraft had been maneuvering at the time, DFCS would have failed

## AFTI F16 Flight Test, Flight 36

- Control law problem led to "departure" of three seconds duration

- Sideslip exceeded 20°, normal acceleration exceeded -4g, then +7g, angle of attack went to -10°, then +20°, aircraft rolled 360°, vertical tail exceeded design load, failure indications from canard hydraulics, and air data sensor

- Side air data probe blanked by canard at high AOA

- Wide threshold passed error, different channels took different paths through control laws

- Analysis showed this would cause complete failure of DFCS and reversion to analog backup for several areas of flight envelope

## AFTI F16 Flight Test, Flight 44

- Asynchronous operation, skew, and sensor noise led each channel to declare the others failed

- Analog backup not selected (simultaneous failure of two channels not anticipated)

- Aircraft flown home on a single digital channel

- No hardware failures had occurred

## AFTI F16 Flight Test

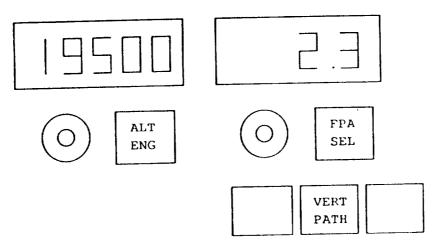

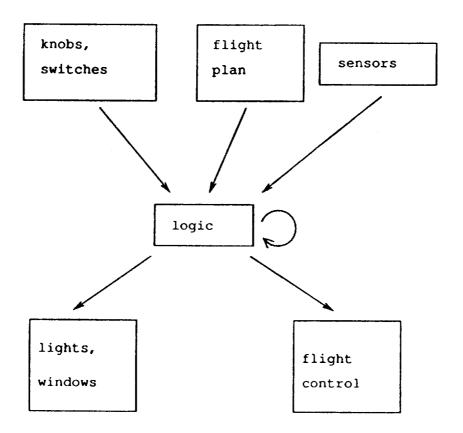

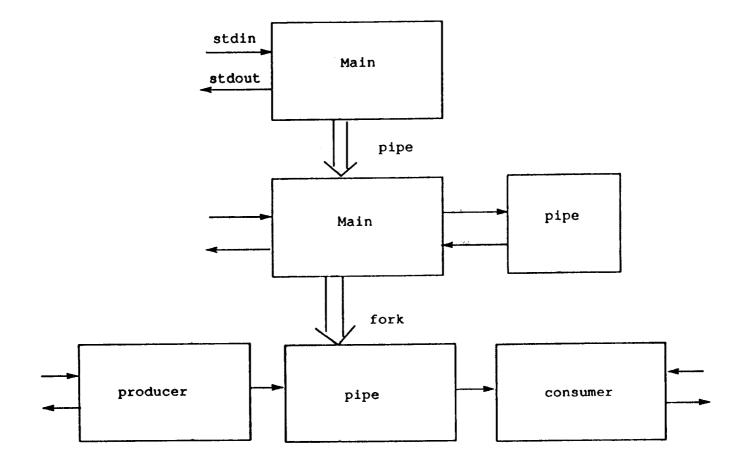

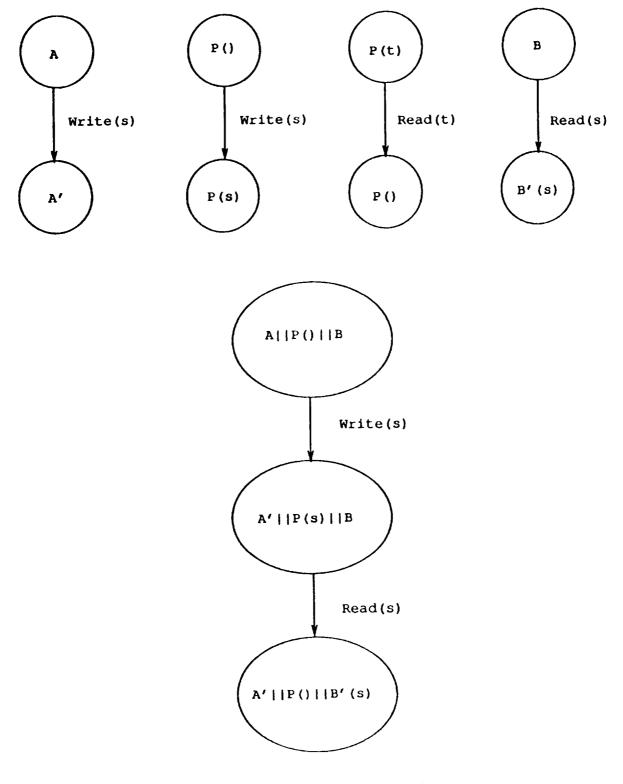

- Repeated channel failure indication in flight was traced to roll-axis software switch